IC测试基本原理与ATE测试向量生成

RZ数据格式,在系统时钟的起始时间T0,RZ测试波形保持为"0",如果在该时钟周期图形存储器输出图形数据为"1",则在该周期的时钟周期期间,RZ测试波形由"0"变换到"1",时钟结束时,RZ测试波形回到"0"。若该时钟周期图形存储器输出图形数据为"0",则RZ测试波形一直保持为"0",在时钟信号周期内不再发生变化。归"1"格式(R1)与RZ相反。

非归"0"(NRZ)数据格式,在系统时钟起始时间T0,NRZ测试波形保持T0前的波形,根据本时钟周期图形文件存储的图形数据在时钟的信号沿变化。即若图形文件存储数据为"1",那么在相应时钟边沿,波形则变化为"1"。NRZI波形是NRZ波形的反相。

在ATE中,通过测试程序对时钟周期、时钟前沿、时钟后沿和采样时间的定义,结合图形文件中存储的数据,形成实际测试时所需的测试向量。

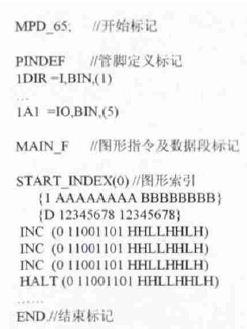

ATE测试向量与EDA设计仿真向量不同,而且不同的ATE,其向量格式也不尽相同。以JC-3165型ATE为例,其向量格式如图4所示。

ATE向量信息以一定格式的文件保存,JC-3165向量文件为*.MDC文件。在ATE测试中,需将*.MDC文件通过图形文件编译器,编译成测试程序可识别的*.MPD文件。在测试程序中,通过装载图形命令装载到程序中。

图4 ATE测试向量格式

2.2 ATE测试向量的生成

对简单的集成电路,如门电路,其ATE测试向量一般可以按照ATE向量格式手工完成。而对于一些集成度高,功能复杂的IC,其向量数据庞大,一般不可能依据其逻辑关系直接写出所需测试向量,因此,有必要探寻一种方便可行的方法,完成ATE向量的生成。

在IC设计制造产业中,设计、验证和仿真是不可分离的。其ATE测试向量生成的一种方法是,从基于EDA工具的仿真向量(包含输入信号和期望的输出),经过优化和转换,形成ATE格式的测试向量。

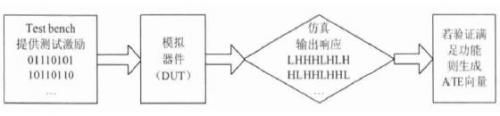

依此,可以建立一种向量生成方法。利用EDA工具建立器件模型,通过建立一个Test bench仿真验证平台,对其提供测试激励,进行仿真,验证仿真结果,将输入激励和输出响应存储,按照ATE向量格式,生成ATE向量文件。其原理如图5所示。

图5 ATE向量生成示意图

2.3测试平台的建立

(1)DUT模型的建立

①164245模型:在Modelsim工具下用Verilog HDL语言[5],建立164245模型。164245是一个双8位双向电平转换器,有4个输入控制端:1DIR,1OE,2DIR,2OE;4组8位双向端口:1A,1B,2A,2B.端口列表如下:

input DIR_1,DIR_2,OE_1,OE_2;

inout [0:7] a_1,a_2,b_1,b_2;

reg [0:7] bfa1,bfb1,bfa2,bfb2;//缓冲区

②缓冲器模型:建立一个8位缓冲器模型,用来做Test bench与164245之间的数据缓冲,通过在Testbench总调用缓冲器模块,解决Test bench与164245模型之间的数据输入问题。

(2)Test bench的建立

依据器件功能,建立Test bench平台,用来输入仿真向量。

Test bench中变量定义:

reg dir1,dir2,oe1,oe2;//输入控制端

reg[0:7] a1,a2,b1,b2;//数据端

reg[0:7] A1_out[0:7];//存储器,用来存储数据

reg[0:7] A2_out[0:7];

reg[0:7] B1_out[0:7];

reg[0:7] B2_out[0:7];

通过Test bench提供测试激励,经过缓冲区接口送入DUT,观察DUT输出响应,如果满足器件功能要求,则存储数据,经过处理按照ATE图形文件格式产生*.MDC文件;若输出响应有误,则返回Test bench和DUT模型进行修正。其原理框图可表示如图6所示。

图6 Test bench验证平台框图

(3)仿真和验证

通过Test bench给予相应的测试激励进行仿真,得到预期的结果,实现了器件功能仿真,并获得了测试图形。图7和图8为部分仿真结果。

图7仿真数据结果

在JC-3165的*.MDC图形文件中,对输入引脚,用"1"和"0"表示高低电平;对输出引脚,用"H"和"L"表示高低电平:"X"则表示不关心状态。由于在仿真时,输出也是"0"和"1",因此在验证结果正确后,对输出结果进行了处理,分别将"0"和"1"转换为"L"和"H",然后放到存储其中,最后生成*.MDC图形文件。

图8生成的*.MDC文件

3结论

本文在Modelsim环境下,通过Verilog HDL语言建立一个器件模型,搭建一个验证仿真平台,对164245进行了仿真,验证了164245的功能,同时得到了ATE所需的图形文件,实现了预期所要完成的任务。

随着集成电路的发展,芯片设计水平的不断提高,功能越来越复杂,测试图形文件也将相当复杂且巨大,编写出全面、有效,且基本覆盖芯片大多数功能的测试图形文件逐渐成为一种挑战,在ATE上实现测试图形自动生成已不可能。因此,有必要寻找一种能在EDA工具和ATE测试平台之间的一种

- 集成电路的电磁兼容测试(06-06)

- 三毫米单片集成电路噪声系数测量技术(07-30)

- 集成电路CDM测试(09-21)

- ADSL集成电路关键参数的测试策略 (10-19)

- 基于MSP430的电机功率因数测量系统(03-20)

- 超声波移动物体检测装置原理简介(05-27)