集成电路CDM测试

简介

集成电路(IC)的静电放电(ESD)强固性可藉多种测试来区分。最普遍的测试类型是人体模型(HBM)和充电器件模型(CDM)。这两种ESD测试类型旨在揭示包含基本ESD控制的制造环境下,电路在ESD应力下的存续情况如何。HBM是应用最久的ESD测试,但工厂ESD控制专家普遍认为,在现代高度自动化的组装运营中,CDM是更重要的ESD测试。CDM应力的大小会随着器件的尺寸而变化。有关CDM的"传统智慧"更认为不需要测试尺寸极小的集成电路,因为峰值电流快

小尺寸集成电路CDM测试

IC CDM Test for Small Devices Robert Ashton 安森美半导体,Marty Johnson 国家仪器,Scott Ward 德州仪器 速变小直至消失。我们在此前的文章中曾指出,极小器件的峰值电流并不像通常认为的那样快速变小直至消失。高速示波器测量显示,即使脉冲宽度变得很窄,极小器件的峰值电流仍令人吃惊地保持高电平。过去,由于这些大峰值电流被忽略,因为使用了场致CDM测试标准所提倡的1 GHz示波器,而场致CDM测试 是最普及的CDM测试形式。

测试小器件时面临的问题

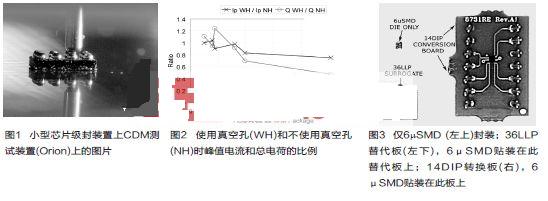

观测到极小集成电路超出预料的峰值电流,对负责测试极小器件(尺寸仅为较小的个位数毫米等级)的ESD测试工程师而言可不是什么好消息。图1显示了置于场致CDM测试装置上的8球栅(ball)芯片级封装。必须接触每个被测引脚的探针(的尺寸)占到整个集成电路尺寸的不小比例。显而易见,移动被测器件并不需要太多的探针接触;只是要求反复调整器件的位置。

在场致CDM测试期间,按惯例要使用真空来固持(hold)被测器件(DUT)的位置。真空通常不能非常安全地固持极小的器件。此外,真空孔(的截面积)占到被测器件尺寸的不小比例,可能会影响器件应力。当真空孔尺寸超过被测器件面积的18%时,应力的大小就开始下降。图2比较了置于真空孔与不置于真空孔上 的器件在峰值电流或完整电荷(total charge)条件下测量得到的应力大小。

在CDM测试期间使用真空来固持器件,由此带来两个问题。首先,它不起作用,即便起作用,也会开始影响测试结果。业界已经尝试使用两种方法来改善小器件的可测试性--将小封装贴在某类夹具(holder)上,或以支撑结构或模板来固持器件的位置。

使用夹具固持小器件

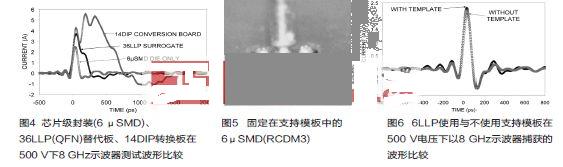

已经在三种条件下使用6 μSMD 裸片来进行CDM测试:仅器件本身、器件贴装在14DIP转换板上,以及在36LLP替代板(Surrogate Board)上,如图3所示。图4显示了这三种条件下以500 V电压采用8 GHz示波器所获得的CDM测试波形。这些结果显示,贴装在电路板上会增加施加给集成电路的应力。36LLP替代板上应力的增加颇为适度,可以视为易于操作性与更可靠测试结果之间的最佳折衷。贴装在14DIP转换板上的应力增加更为严重,大概不是一个可接受的折衷办法。好消息是36LLP替代板实际上比测试期间会移动的14DIP转换板更易于操作。

支持模板

第二种处理小型集成电路的方法是使用支持模板。业界存在关于支持模块这种方法的顾虑:由于小器件周围有介电常数较高的材料,介电的存会在多大程度上改变集成电路与场板(field plate)之间的电容?被测器件与场板之间的电容是被测器件上应力大小的决定因素。图5显示了固定在CDM装置中一个模板内的6 μSMD封装。此时被测器件位于绝缘体中精心加工的孔,而绝缘体位于CDM装置使用真空的场板中。图6显示了6LLP封装使用与不使用FR4支持模板时以8 GHz示波器捕获的波形。此图显示这模板在测试条件下仅为集成电路增加极小的应力。

结论

使用场致CDM方法来测试极小集成电路存在不少挑战。将极小器件贴装在电路板上能够大幅改善测试的操作,但必须密切注意,使电路板不要太大,否则器件会遭受比没有使用电路板来测试时严重得多的应力。使用模板来在测试期间固持器件的位置所带来的应力增加极小。制造在测试期间能稳固维持器件的模板将是一项挑战。

- 集成电路的电磁兼容测试(06-06)

- 三毫米单片集成电路噪声系数测量技术(07-30)

- ADSL集成电路关键参数的测试策略 (10-19)

- 基于MSP430的电机功率因数测量系统(03-20)

- 超声波移动物体检测装置原理简介(05-27)

- 分析PCB电路板的测试仪功能原理和应用特征(09-12)