嵌入式存储器的测试及可测性设计研究

引言

近年来,消费者对电子产品的更高性能和更小尺寸的要求持续推动着SoC(系统级芯片)产品集成水平的提高,并促使其具有更多的功能和更好的性能。要继续推动这种无止境的需求以及继续解决器件集成领域的挑战,最关键的是要在深亚微米半导体的设计、工艺、封装和测试领域获得持续的进步。

SoC是采用IP复用技术的一种标准设计结构,在多功能电子产品中得到了广泛的应用。SoC的典型结构包括CPU、存储器、外围逻辑电路、多媒体数字信号编解码器和接口模块等。现在的SoC中,存储器通常占据整个芯片的大部分面积,并且可能包括各种类型的嵌入式存储器,如DRAM、SRAM及Flash存储器等,可满足不同的应用需要。目前SoC设计要求存储器的容量不断地增大,嵌入式存储器在SoC中所占的面积百分比也随之不断增加。另外,SoC的复杂度不断地提高而集成电路工艺尺寸在不断减小,这就导致嵌入式存储器的制造缺陷比例也不断地增加。因此嵌入式存储器的故障率对于SoC的总成品率的影响越来越大,而保证低故障率的关键是高效率和高故障覆盖率的嵌入式存储器测试方案。

在我国,集成电路测试及可测性设计,特别是存储器的测试研究相对国际上的研究比较落后。目前,我国自主研究的测试算法以及开发的测试设备还没有形成产业化,还不能与国际上先进的集成电路测试设备相抗衡。而近几年来,我国在集成电路领域加大了投入,集成电路产业也得到了长足的进步。

集成电路测试也是一个知识密集型的高投入领域,一直是我国集成电路产业发展的制约因素。半导体工业成本发展的特点就是它的单位功能制造成本以每年平均25%~30%的比例下降,而测试成本却以每年平均10.5%的比例提高。随着集成电路复杂度的不断提高,为其设计的测试电路也越来越复杂,测试电路占用的芯片面积及设计制造成本也变得更高。

本文对嵌入式存储器的测试及可测性设计进行研究总结,为我国存储器测试的研究以及集成电路测试产业的发展奠定坚实的技术基础。

嵌入式存储器测试方法

半导体存储器自20世纪60年代开始设计生产以来,在设计结构、产品的性能和存储的密度等各方面发生了巨大的变化,现在嵌入式存储器技术的发展已经取得了很大的成就,并被广泛应用于各类基于SoC芯片设计的电子产品中,已经成为大多数电子系统中必不可少的组成部分,在人们的生产生活中起到了举足轻重的作用。嵌入式存储器的测试方法主要包括以下三类:

存储器直接存取测试

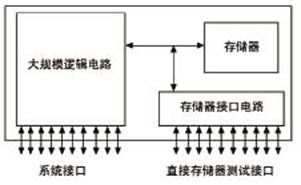

此类测试方法把嵌入式存储器部分从整个系统中分离出来,由专用的存储器测试电路连接到存储器接口上对嵌入式存储器进行测试,系统框图如图1所示。

图1 存储器直接存取测试

专门设计的存储器接口电路仅在需要对存储器进行测试时才通过I/O多路选择器选择使用,并利用测试仪产生的存储器测试向量对存储器进行测试。因此这种测试方法可以从芯片的封装引脚直接对嵌入式存储器进行测试,也可以直接对存储器测试的逻辑状态和存储器运行的过程进行监控和测试,可以方便地实现嵌入式存储器的多种测试算法。但这种测试方法也存在不足之处,对存储器进行测试的测试向量需要串行化后才能通过I/O端口的多路选择器送入存储器接口电路,这样不仅增加了测试的复杂度,而且还增加了测试的时间。

片上微处理器测试

这种测试方法利用SoC上的微处理器构造测试系统对嵌入式存储器进行测试。首先,选择对嵌入式存储器进行测试的测试算法,利用微处理器的汇编语言编写相应的测试算法程序;然后,通过微处理器汇编语言的编译器得到可执行代码;接下来,将可执行代码下载到系统中,通过微处理器的运行产生相应的测试向量,并按照测试算法对嵌入式存储器进行测试。测试的结果由微处理器进行比较评估,也可以由专门设计的结果处理电路进行结果判定。

这种测试方法的优点是利用SoC现有资源,而不需要设计额外的测试电路,也不需要对现有电路进行任何修改,因此不会增加额外的面积开销,也不会降低性能。这种测试方法可以采用任何一种测试算法对嵌入式存储器进行测试,可以提供全故障诊断和进行全速测试。但是这种测试方法也有一定的缺点,首先芯片中的嵌入式存储器部分或者全部与微处理器不相连,需要有专用的接口电路对测试算法的二进制代码进行处理,其次不同测试算法的编程和程序修改需要大量的时间和人力,还有这种测试方法不能测试存储测试程序的存储器。

存储器内建自测试

存储器内建自测试(Build-in Self Test, BIST)是近几年里大量应用于存储器测试领域里的一种非常重要的技术。这种技术利用芯片内部专门设计的BIST电

- 复杂系统级芯片的软件/硬件协同验证(11-06)

- 采用多内核无线虚拟系统原型的系统级调试(11-07)

- 嵌入式测试方案及高速测试技术(03-10)

- 低功耗制造性测试的设计-第二部分(01-29)

- SoC的发展将使测试与测量设备嵌入芯片(10-21)

- 基于PSoC的防高压电容测量设计与实现(03-27)