基于边界扫描技术的电路板可测性设计分析

U0和EMU1接地。

另外,如果器件除了支持取样/预载(SAMPLE/PRELOAD)、互连测试(EXTEST)、旁路(BYPASS)这些IEEE 1149.1强制的指令外,还支持IDCODE、CLAMP、HIGHZ等指令,就能给测试带来更多方便。有些器件,内部功能不同但有着相同的封装,IDCODE指令能对此加以很好的区分,确保正确的器件安装在正确的位置。CLAMP和HIGHZ指令可以使器件的输出引脚处于一个固定状态,从而避免总线竞争。

2.1 扫描链完整性测试

扫描链连接完毕后,为保证后续工作的进行,要测试它的连通性,包括BYPASS测试和IDCODE测试。在TAP控制器处于复位状态时,BST电路无效。器件已处于正常工作状态,这时指令寄存器也已完成了初始化。如果器件支持IDCODE,则初始化的指令为IDCODE,否则为BYPASS。在TCK控制下,IDCODE或BYPASS寄存器中的内容就从TDO端口移出,测试软件将读到的数据与正确数据对比,从而判定扫描链的通断和器件型号的正确性。对于BYPASS测试,器件的BYPASS寄存器初始值为0;对于IDCODE测试,器件的标准IDCODE从BSDL文件中提取。

2.2 包含非边界扫描器件的互连测试

对于一个电路板来说,相当部分的器件都是非边界扫描器件,如何有效利用扫描链来测试连接在边界扫描器件之间的非边界扫描器件是提高故障覆盖率的关键。可以说,故障覆盖率与边界扫描器件的边界扫描寄存器提供给非边界扫描器件的可控制性和可观测性的程度息息相关。

2.2.1 可控制性的提高

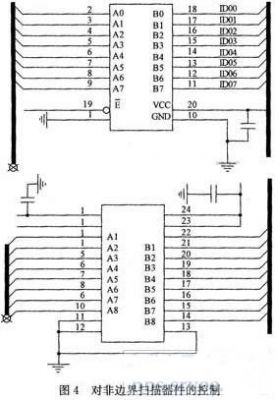

为了增加可控制性,对于非边界扫描器件的重要的控制信号,如片选端和使能端,尽可能地直接控制,或者通过边界扫描器件的边界扫描单元进行控制。这样在测试时,为了避免信号冲突可以把相应的器件禁用或者改变信号输入输出的方向。如图4所示,器件N17(SN74LVC4245A)的/OE端和DIR端与N14(EPLD)的引脚相连。N50(74F245)的/E端也受N14控制,而DIR端接地,N50的/E端选通时,固定的B端为输入而A端为输出。N17和N50的A端引脚共享VXI总线的D00-D07,但B端引脚分别连在不同的总线上。如果N17的/OE端选通,DIR端置0时,A端为输入,与N50的A端为输出相矛盾;DIR端置1时,B端为输入,不同的总线信号发送到同一引脚上,引起冲突。因此,通过N14的BS引脚控制N17和N50,让两个器件不同时选通,使测试顺利进行。

2.2.2 可观测性的提高

为了增加可观测性,本文要给测试软件提供这些非边界扫描器件的基本信息,如器件的电源Vcc和接地GND引脚、I/O引脚的性质(是输入、输出、三态输出还是双向的)、器件的逻辑功能等,也就是对非边界扫描器件进行建模,编写测试软件能识别的MODEL。以74F245为例,其MODEL如下:

在此MODEL中,描述了器件的引脚性质及各种状态下的逻辑功能。MODEL被分成了若干PART,要根据电路板上器件的具体连接情况来选取相应的PART。对于N50和N51来说,因DIR引脚接地,固定为低,我们就选取PARTBtoA_with_DIR_fixed

在做互连测试时,建模的器件越多,故障覆盖率就越高。本文做了一个对比实验。如图5所示。N14的109、110和111这3个引脚分别与3个上拉电阻相连,同时与插针J6相连。通过跳线可以使3个引脚处于001~111这7个状态中的某一个,从而确定被测板电路响应VXI总线中7根中断线中的某一根。在向测试软件输入被测板的信息时,我们默认109~111这3个引脚正常状态为逻辑高。那么,当我们用跳线将J6的1、2 脚短接时,就人为制造了N14的109脚与地短路的故障。

第一阶段,本文只对电路板上的179个电阻进行了建模,测试得到的与边界扫描器件引脚相关的故障覆盖率为56.78%,没有检测到故障。第二阶段,本文在第一阶段的基础上又对39个与边界扫描器件相连的非边界扫描器件进行建模,测试得到的故障覆盖率为67.03 %,有了明显提高,且故障检出,结果显示如图6所示。

3 结束语

复杂数字电路板的可测试性设计是电路和器件设计领域研究的重要课题。本文介绍了通过在复杂数字电路板中设计和利用器件的边界扫描结构,提高电路板的可测试性,及通过增加边界扫描器件对非边界扫描器件的可控制性与可观测性,获得更高的故障诊断覆盖率的方法。

边界扫描技术实现了可测性设计的一次变革,但它并不能解决所有的可测性问题。边界扫描的长处在于器件引脚之间的互连测试。由于TCK速度的限制,边界扫描对于器件内部的动态故障显得无能为力。而自建内测试技术(BIST)则是针对器件功能性测试的。把BIST结构置入芯片内,结合IEEE 1149.1中可选择的RUNBIST指令可以达到高的故障覆盖率。因此,要全方位地对故障类型进行考虑,利用现有的DFT技术,混合采用传统的ICT,取长补短

- 集成电路的电磁兼容测试(06-06)

- 低功耗制造测试的设计-第一部分(01-29)

- 基于PXI和GPIB总线电路测试系统的开发与设计(01-14)

- 基于单片机设计的小电阻测试仪(01-13)

- 分析TDA7294大功率集成功放电路的测试原理(02-27)

- 大容量存储器集成电路测试(12-23)