逻辑分析仪为I2C信号量测提供完整方案

时间:01-16

来源:3721RD

点击:

意图。

若采用低通滤波(Low-pass filter)的做法,是可以滤除杂讯,但又使得可能造成线路问题的高频杂讯也同时被滤掉了。无论如何,这都不是适当的解决方案。

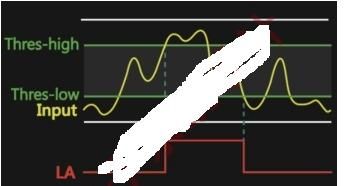

而图六则是启用了舒密特触发电路之后的画面,此架构采用了两组触发电压,分别为 Thres-high 与 Thres-low。两个电压间,就是所谓不转态区域,在这个区间内,不管讯号怎么改变,都不会影响逻辑判断。 这样,就可以正常的撷取到I2C 讯号,且真正的高频杂讯也不会漏掉,也符合I2C 晶片设计规范。

图六 逻辑分析仪采舒密特电路触发模式示意图。

堆叠示波器可同时看到I2C数位与类比讯号

在使用了逻辑分析仪所提供的I2C汇流排触发与分析功能后。撷取下来的波形开始要进行问题分析阶段,常常很多专案都是软硬体共同合作,参与的人很多,若无法同时看到对应的类比讯号,对于厘清问题帮助不大。尤其是线路造成的问题,数位讯号并无法清楚地呈现出问题点。

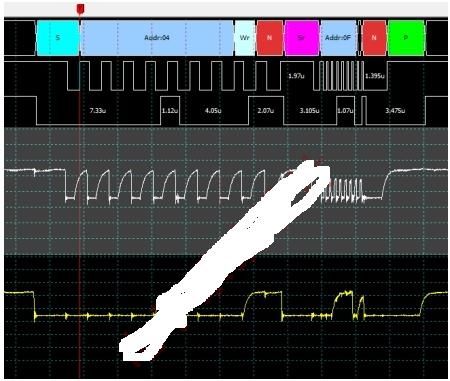

但是,单纯逻辑分析仪堆叠示波器并没有任何帮助,因为大部分的时候逻辑分析仪可以抓的时间长度会远大于示波器,这样,即使示波器显示波形出来,也不在正确的位置上。唯有透过逻辑分析仪的触发功能进行讯号定位。这样抓到的类比讯号才是有意义的。图七就是利用堆叠并设定触发之后同时抓到数位与类比讯号。 使用者可以将它发送给需要看波形的人,I2C汇流排数位解码的部分可让使用者快速理解他所看到波形。 而类比讯号的部分,则忠实的呈现出波形的原貌。两者这样的结合,成为最佳的量测方案。

图七 逻辑分析仪与示波器堆叠示意图。

- 基于虚拟仪器的网络虚拟实验室构建(11-06)

- 信号完整性基础系列之十一——理解力科SDA的三种抖动分解(01-05)

- 数位仪表设计-HY12P65简化可携式电量测量设计(04-03)

- 关于基于FPGA平台的手持式频谱分析仪的实现原理(01-06)

- 双T型功率振荡器用作直流偏置交流源(08-10)

- 基于双DSP的电力系统谐波分析仪的设计(12-23)