空间谱估计测向系统设计

估计测向方法需经较为复杂的计算才能得到待测信号的到达方向,因此性能优异的高效测向算法和高速数字信号处理终端就成为这种测向技术的核心。从原理上考虑,一台通用微机可用于信号处理终端。当要求测向过程实时或准时时,则应采用高速数字信号处理器完成信号处理终端的任务。

3.2 空间谱估计算法的硬件实现方案

现代数字信号处理方案多采用FPGA和通用DSP的混合设计,即DSP+FPGA的设计方案。用FPGA设计协处理器处理大量、规则的计算,而利用DSP的灵活性处理复杂不规则的计算,从而使整个系统性能达到最优。

对空间谱估计测向中的MUSIC算法分析可知,MUSIC算法可分为:求解协方差矩阵,对协方差矩阵特征分解和谱峰搜索。其中,求解协方差矩阵是一种包含大量而又规则计算的算法,且运算的数据直接从接收机的A/D转换器输出得到,可采用定点计算方式,适合采用FPGA实现。FPGA具有可编程和现场配置的特点,利用与器件相应的CAD软件,实现用户规定的各种特定功能,具有较高的灵活性。设计者可将其视为一个由若干与非门构成的阵列,各与非门之间通过一定的方式相连接,实现特定功能。

实现协方差矩阵的特征分解可采用雅可比算法。该算法中。数据的动态范围很大,用定点计算会发生溢出,并且也无法满足精度要求,所以只能采用浮点计算;雅可比算法除包含大量的乘法、加法外,还有开方、除法等不太规则的计算。因此,用于实现特征分解的雅可比算法不宜采用FPGA实现,而应采用DSP实现。DSP类似于通用微处理器CPU,但又有其针对数字信号处理的特点。其与通用微处理器不同之处在于:采用哈佛结构,程序和数据分开存储;采用一系列措施保证数字信号的处理速度,如对FFT的专门优化。因此DSP数字信号处理能力大大优于通用微处理器,同时还具有通用微处理器系统灵活度高,计算可编程控制的特点,可适用于各种复杂的信号处理。

因此,MUSIC算法的硬件实现可采用DSP+FPGA来实现,即定点计算和浮点计算混合的方案。FPGA实现求解协方差矩阵,可采用定点计算方法,然后把得出的数据送入DSP,将其定点转换为浮点,用浮点计算方式计算特征分解和谱峰搜索。

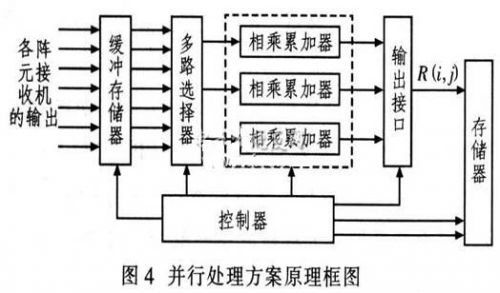

求解协方差矩阵时有串行和并行两种方案。串行方案主要是以节省资源为优先考虑的一种方案,可用于那些对实时性要求不太严格的应用中;并行解决方案主要是以处理速度为优先考虑的一种方案,可用于那些对实时性要求较高的应用中。图4给出并行处理方案的原理框图。

并行方案与串行方案的区别在于:并行方案使用多个并行相乘累加器进行计算。这样可有效提高整个系统的处理速度。并行处理的方案应当做到使各处理器的负载平衡,对于含8个阵元的测向系统,需要求出36个元素的值,因此可选用2,3,4,6,12,18,36个相乘累加器的不同的并行处理方案。显然相乘累加器越多,处理速度越快,但其成本也高。

4 结论

在空间谱估计测向系统构成、工作原理、某些关键技术及硬件实现的基础上,介绍基于相关矩阵特征分解的MUSIC算法原理及其硬件实现方案。空间谱估计技术对雷达信号侦察测向的前景良好,具有研究价值。

- 浅谈数字化宽带测向系统中的相位差测量及误差(12-26)

- ADSP-TS201在无线电测向系统中的应用(05-31)