ADuC7128实现宽频带相位测量系统

作。这样,计数器T1 上的累计值就是两个方波间隔的脉冲数n,如果已知T1 的计数间隔Δt',即可知两个方波的时间间隔Δt:

从而通过公式( 8) 即可计算出两输入信号的相位差θ。

2. 2 软件设计

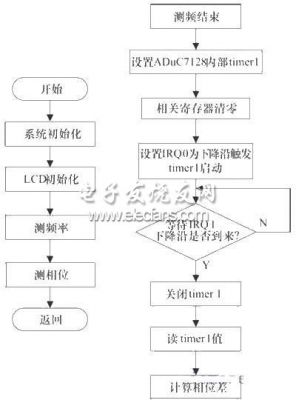

本系统的软件设计主要是完成系统初始化、内部数据处理、数据结果显示等功能。图4 是系统的主程序和相位测量流程图。

图4 主程序和相位测量流程图

3 测试结果与分析

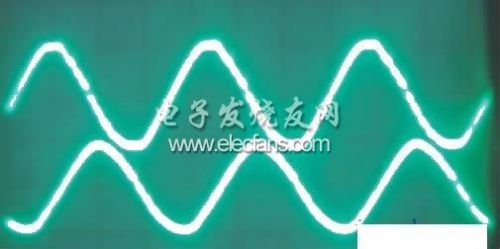

两路同频输入信号是由一个相位差可调节的高精度信号源产生。当输入信号频率小于30 kHz时,由ADuC7128 内部计数器直接计数,经过数据处理后得出相位差。输入信号在进行过零比较时,由于两路输入信号之间的电平不相等所引起的幅相误差,使得整形后产生的方波有所失真。图5 是两路输入信号为100 kHz,相位差75°的正弦波信号,经过频率变换及滤波整形后,两个信号的相位保持不变,频率变为30 kHz、幅度线性变化,如图6 所示。

图5 两路相位差75°的正弦波信号

图6 两路相位差75°的方波信号

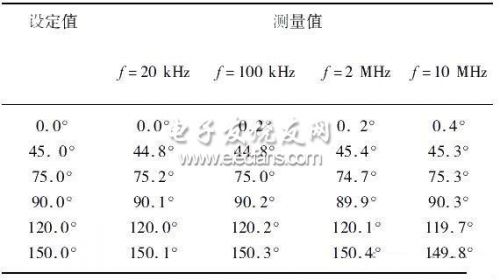

随机抽取四个不同频率的输入信号,分别在相位差为0 ~ 150°的范围内进行测试,测试结果见表1。

测量结果表明该系统的最大测量不确定度为± 0. 4°,基本满足了预期≤0. 5°的设计要求。主要误差源是ADuC7128 内部计数器只能进行整数计数,而引起的± 1 的计数误差,该误差可以采用多次测量求平均值的软件方法进行修正。同时,两路信号通道内部硬件电路结构存在差异,也是造成测量误差的原因,解决此类误差只能在设计对称结构的硬件电路时,尽量选用相同的元器件。

4 结论

该系统能够完成输入信号在0 ~ 10 MHz范围内的相位测量,测量分辨率可达0. 1°,通过使用ADuC7128 芯片内部DDS 模块,节省了硬件成本,同时也降低了电路设计的复杂性,增加了系统的可靠性。试验表明,该系统设计方案可行、测量结果准确。如果直接选择主频较高的微处理器或者通过时钟倍频的方法提高计数脉冲速度,在此设计方案基础上,就能够进一步拓宽相位测量的频带。

.

- DDS函数信号发生器的优点(09-28)

- 基于DSP与AD9852的任意信号发生器 (11-03)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于AD9858的线性调频源设计(11-03)

- 基于DDS的高分辨率信号发生器的实现(11-04)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)