基于姿态测量的微型存储系统的设计

本次设计的微型姿态存储器测试系统的另一个主要突出点在于它的微型化 ,整个的记 录器的各个芯片都采用了小型化的贴片封装,电路板采用了四层板工艺制作,中间分别为电 源层和地层,不仅大大较小了记录器的体积,同时对信号的隔离和抗干扰性也起到了一定的 积极作用。

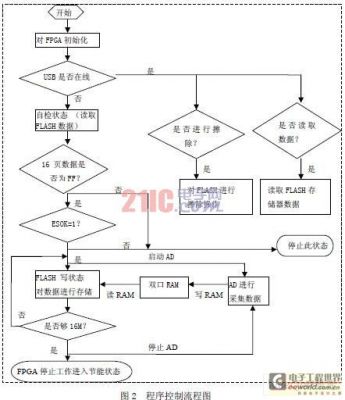

3 逻辑流程图设计

流程图见图2 所示,整个过程由过载开关启动电源控制芯片以启动整个FPGA 的控制 时序,复位模块由上位机复位,上电自动复位和软复位组合而成,当启动整个系统时,首先 要对系统初始化复位,同时定义一个触发信号"esok"使初始化为"0",以便触发控制单元, 使系统进入自检状态,在自检模块中,FPGA 首先要从FLASH 存储器第六页连续读取16 页的 数据,并判断数据是否为"FF",如果不是,则存储器内有数据存在,系统将停止在这个状 态;如果是则触发信号"esok"为"1" 以启动A/D 采集数据模块和FLASH 存储数据模块, 此时,中心控制模块在响应采集模块的中断使A/D 模块以16K 的采样率往FPGA 内部的双口RAM 写数据,同时FLASH 存储模块在中心控制模块下,判断并推进RAM 的地址以读取RAM 的 数据,在数据不断写入FLASH 存储器的同时判断数据容量是否达到指定的数据量,如果没有, 则返回到FLASH 写状态继续存储数据,一旦达到,系统则触发一个信号来控制电源模块关闭 电源,使整个系统停止工作,以减小耗电量。当插上读数口时启动USB 在线,在上位机的控 制下,对FLASH 存储器进行读取操作,以便对数据进行事后分析和处理。

结束语

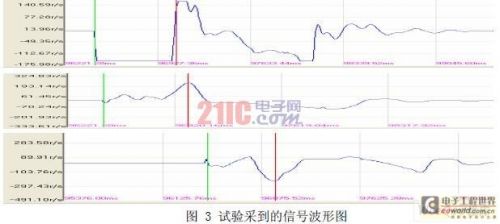

该微型姿态存储测试系统工作性能良好,在抛撒试验中得到如图3 所示的信号,达到了 理论要求,成功的完成了飞行体姿态参数的采集和存储,通过多次试验证明,该微型测试系 统具有一定的工程应用性并对其他测试设计有着重要参考意义。

- 采用CompactDAQ平台提高USB数据采集应用的性能(01-17)

- 基于FPGA的USB2.0虚拟逻辑分析仪的设计与实现(01-18)

- 高速串行数据链路的自动化一致性测试(04-15)

- 基于LABVIEW的USB接口多路高速数据采集系统的设计(11-24)

- 基于AVR USB接口的温度测量系统下位机设计(03-01)

- 理解下一代数据采集技术(05-12)