使用NI VeriStand 2010创建分布式系统

概览

分布式系统有多种形式。例如,在与中央处理器不同的位置处理输入和输出(I/O)的方法通常称为分布式I/O。另一个例子是为单系统添加多个处理器,对运算分布式化。本文讨论了如何使用NI VeriStand 2010创建分布式处理和I/O系统,其中包含将开发分布式系统变得更为有效和有力的许多特性。例如飞机、汽车或其他工业项目中的控制系统常常需要比单个处理器板卡和机箱所能提供的更多的计算能力和I/O来 进行监视、测试或仿真。本白皮书详细介绍了如何创建可扩展、分布式的同步系统,满足大型硬件在环(HIL)或实时测试系统的需求。NI VeriStand 2010是用于配置包括HIL测试系统在内的实时测试应用的即用型软件环境。利用NI VeriStand 2010特性,无需对软件体系结构进行设计、编程和维护,就可以创建系统。

分布式系统需求

您通常可以将大型系统分解为多个不同组件,独立实现每个组件的硬件和软件。要提供更高计算能力和I/O容量,您可以在不同硬件上实现系统的各个组件。

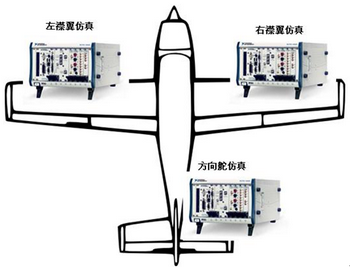

例如,飞机的襟翼、缝翼、方向舵、引擎、副翼等都需要仿真和测试。可以如图1所示,将系统分解为多个硬件部件,从而使用模块化方法。

图1. 可以用多个PXI系统仿真飞机组件

系统级集成特性

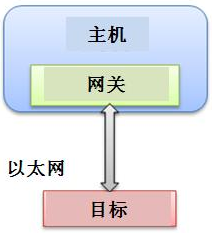

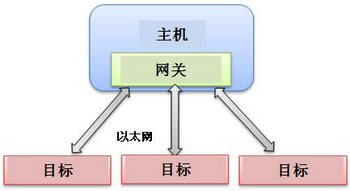

使用NI VeriStand 2010,一个或多个操作者(主机)计算机可以在最少用户配置的情况下,与一个或多个实时执行目标进行通信。NI VeriStand处理操作者计算机(主机)与实时执行目标之间的通信。图2给出了包含主机和目标的简单拓扑结构。

图2. 简单拓扑结构

主机用于和目标通信的组件是NI VeriStand Gateway。虽然通信管理是自动完成的,它是理解大型拓扑结构所需的重要概念。

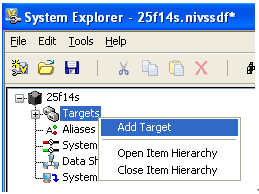

您可以方便地在NI VeriStand 2010系统浏览器中将目标添加到拓扑结构中。

图3. 在系统浏览器中添加目标

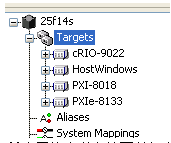

单个系统定义文件可以包含无限多个目标,甚至可以混和不同目标类型。

图4. 单个系统定义文件可以包含多个目标

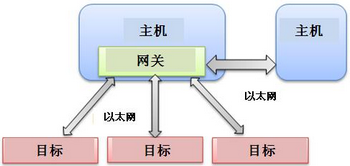

每个目标有自己的专用硬件和软件配置,所有目标可以通过单个网关实现部署和交互。

图5. 可在单个主机上部署多个目标并进行交互

通过与另一个主机网关进行通信,其他主机计算机可以与相同的拓扑结构进行通信。

图6. 多个主机与多个目标拓扑结构

要完成这点,其他主机只需要修改NI VeriStand网关地址为远程主机即可。其他应用程序保持不变。

在分布式计算机之间共享数据

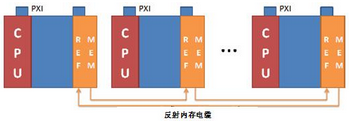

要让分布式系统如同单个系统一样工作,必须在系统组件之间共享数据。这是让不同部分可以一起工作的关键要素。通常可以使用反射内存接口实现。

反射内存网络是实时本地局域网(LAN),每个计算机总是拥有共享内存集合的最新本地复本。这些专用网络是为了提供高确定性的数据通信而专门设计的。可以提供多种分布式仿真和工业控制应用所需的高级定时性能。反射内存网络获益于通用数据网络,是不同需求推动下产生的完全独立的技术,适用于要求确定性、简单实现和软件负荷小的应用程序1。

反射内存为NI VeriStand提供了在多个目标之间共享数据的能力,并且满足了整个系统的性能与确定性需求。使用反射内存,仿真模型可以分割在不同的目标系统上同时执行。输入与输出数值通过反射内存在不同目标系统上共享。GE Fanuc反射内存板卡本地支持NI VeriStand 2010。NI VeriStand 2010的许多组件可以使用反射内存无缝创建多目标系统。

此外,NI VeriStand 2010将数据在目标之间自动分步用于不同的用途。例如,您可以配置激励(测试)档案运行在需要目标B数据的目标A上。NI VeriStand 2010在目标之间自动创建并激活链路获取数据。这可以在无需用户配置的情况下自动完成。

图7显示了包含反射内存板卡的实例系统。

图7. 使用反射内存的多个机箱

同步分布式系统

在设计系统时,考虑时序与同步的需求是十分重要的。如果分布式硬件不进行同步,输入和输出的采样将不同时发生。另外,随着时间的推移,漂移会导致系统的一个组件比另一个组件得到更多采样,尽管它们被配置为同样的速率。如果仿真是您的目标,这将导致问题。例如,两个襟翼仿真可能处于不同的时间状态。另外,因为数据并非来自相同的时间点,数据记录和分析将被破坏。

同步基础概要介绍了例如时钟漂移和时钟偏差的许多细节。

分布式系统的同步包括硬件同步和软件同步。您可以选择性地将整个系统与GPS或IRIG等外部时间参考进行同步。

硬件同步

硬件同步意味着系统的每个硬件共享一个硬件参

考时钟,用于定时和开始I/O任务。系统中的每个硬件都利用相同的硬件参考时钟生成其自己的时钟,每个硬件都在相同的时间开始。

常见的

- 采用模块化仪器,对新兴音频和视频应用进行测试(02-19)

- NIDays2008新技术新体会——多核技术下LabVIEW编程(10-21)

- 你知道吗?——NI也是08年北京奥运会的幕后功臣之一(10-17)

- LabVIEW8.6有哪些新亮点?(10-17)

- 使用虚拟仪器降低测量成本(11-06)

- NI FlexRIO适配器模块开发工具集(MDK)包含哪些内容?(01-06)