基于ARM9的高速数据采集系统的实现

m),则有t1+t2+t3+…+tm一1/fs,既所有通道存储时间之和为采样周期。

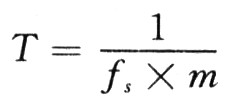

假设t1=t2=…=tm=T,则各通道存储时间相同的条件为:

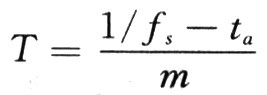

从实际角度出发,在一个采集时钟周期内还有其他的时间消耗,如保持时间和转换时间等,假设其他时间消耗为ta,则:

如果fs的占空比为1:1,根据ADC实际工作时的情况,可以近似认为ta=1/(2*,fs),既在一个采集周期中只有半周期的时间可供存储数据,则单个通道的存储时间:

根据上面的设计可以实现单采样周期内多路数据存储。

3.6 系统抗干扰设计

(1)电源设计方面

根据高速电路设计理论,AD采集系统中的电源应当采用线性电源,以避免开关电源引入噪声。为了降低电源阻抗,减小噪声对电源的干扰,通常采用电源层设计,尽可能增大电源面积。在设计每个芯片的供电电路时,在每个芯片的电源附近并联去耦电容和旁路电容。去耦电容为芯片提供局域化的直流。旁路电容可以消除高频辐射噪声和抑制高频干扰。

(2)接地技术方面

高速数据采集系统的模拟地和数字地应严格分开,最后单点共地。共地点通常选择在ADC芯片管脚所需电流最大的位置,这样可以使大电流对地回流最近,以避免对模拟电路的干扰,提高系统的采集精度。

模拟地和数字地可以通过磁珠连接,由于磁珠的高频阻抗大,而直流电阻为零,能够滤除高频电流减少地线上的高频噪声。

4 结语

高速数据采集系统一直是测控领域内研究的热点,本文就基于ARM9的高速数据采集系统的结构,详细讨论了系统时钟电路设计、模数转换器的选择、模拟信号调理电路的设计、硬双缓冲实现连续采集存储、多路同步采集存储的时序分析,系统抗干扰设计等关键技术。经实践证明,该设计方案效率是很高的。

在高速的数据采集过程中,要求数据存储和S3C2410读数据同时进行,在相关文献中提出了一种基于软件系统双缓冲模式的存储技术,但是经过分析发现其在解决连续存储和读数的同时也降低了微处理器的性能。在本设计中提出的基于硬件的双缓冲模式可以很好地解决这个矛盾,其工作原理如图2所示。

- 基于嵌入式Linux的磁场测量系统(03-26)

- 基于嵌入式Windows CE5.0的无线监控系统研究(03-26)

- 基于嵌入式ARM9的墙面平整度检测仪研究与实现(10-18)

- 基于ARM9和3G网络的社区温湿度远程监测系统研究(10-18)

- 基于嵌入式系统的远程参数测量的方法和实现(10-31)

- 基于ARM9和USB摄像头的网络视频采集系统设计(03-30)