利用NI LabVIEW的并行化技术来提高测试的吞吐量

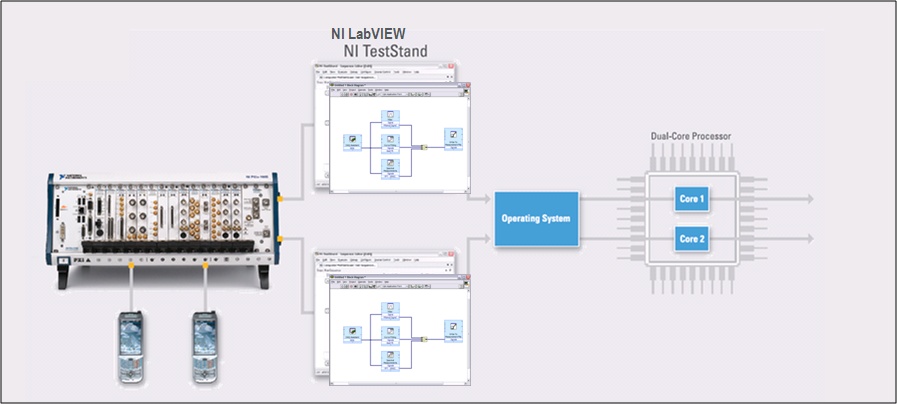

图4.PCI Express和模块化仪器为并行化测量提供了可调整的模型

在PXI Express模块采集数据时,它通过专用的PCI Express通道将数据从板上存储器写入到硬盘驱动器或者系统存储器中。当数据被传输到系统存储器中时,LabVIEW应用程序可以访问数据,而且如果与多核处理器配合使用,那么从信号到最后测量的并行化测量就实现了。

并行化测试

利用多核处理器、PCI Express总线和LabVIEW软件,用户可以创建并行化的测量系统,它们能够同时测试一个待测单元(UUT)。但是,并行化测试的定义是指多个待测单元同时接受测试。替代方案是顺序化地测试待测单元。虽然并行化测试可以显著地降低总体的测试时间、增加测试吞吐量,并且改进仪器的使用方法,但是开发并行化测试系统的复杂性是非常巨大的。开发测试管理软件以实现同时测试多个待测单元,需要理解底层的操作系统并行化工作的原理(如Windows的临界代码段)有所了解,不仅需要周密地考虑在多个待测单元间进行仪器共享,而且要避免冲突或者死锁。

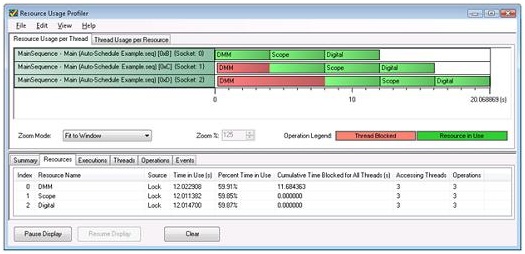

从头开发自定义的并行化测试系统的替代方案是使用即时可用的测试管理软件,如NI Teststand。该软件使用内建的特性,对并行化测试系统开发中底层的复杂度进行了抽象化,用于在多个线程中执行并行化的测试序列,同时对操作系统和仪器资源进行管理。另外,用户可以使用NI Teststand Resource Profiler工具来理解仪器的使用和并行化测试系统的执行,进而降低测试时间并提高吞吐量。Resource Profiler工具可对测试系统执行进行分析,并且确定仪器的瓶颈来帮助用户优化测试代码,区分未来仪器投资的优先顺序。如图5所示,profiler工具实时显示了仪器和其它资源的使用情况。

图5. NI TestStand Resource Profiler工具帮助开发者理解并行测试系统的执行, 进而提高了系统的吞吐量

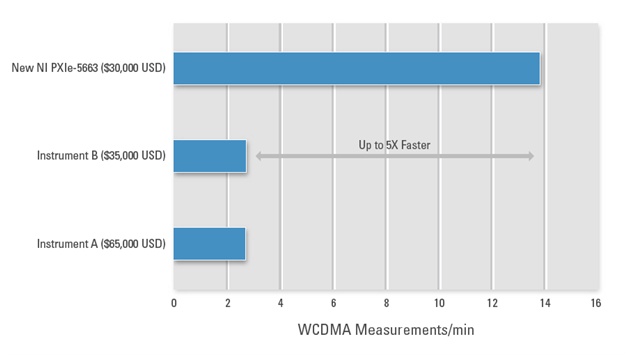

为了解释采用并行化测试构架的性能优势,请考虑比较使用PXI平台和传统仪器来实现基本的WCDMA测试序列。与W-CDMA测试标准一致,基准应该包含测量(如相邻信道功率(ACP)、占用带宽(OBW)、补偿累积分布函数(CCDF)和误差向量幅度(EVM))的时间和精度。如图6所示,在测量速度方面,基于NI TestStand、LabVIEW和PXI平台的并行化测试平台提供了5倍的改进。这可以显著地节省终端用户的开销。需要了解更多关于基准分析的信息,请查阅《射频基准比较白皮书》。

图6. 相比于传统仪器,基于LabVIEW、NI TestStand和PXI的NI并行化测试平台,提供了5倍的测量速度改进和更高的精度

完成并行测试构架

多核处理器、FPGA和PCI Express正在改变现代PC机的版图,并帮助LabVIEW图形化编程根据工程师应用逻辑的数据流向,实现真正的并行化处理和并行化测量。利用NI TestStand软件,可以完成并行化的测试构架。具有此结构的测试系统利用PCI Express提高了数据吞吐量,使用LabVIEW、多核处理器和FPGA增强了处理能力,最后利用NI TestStand软件降低了每个待测单元的总体测试时间和费用。

- 基于LabVIEW RT的自定义流程测控系统(10-30)

- 基于LabVIEW的语音分析平台的实现(10-30)

- 基于示波器卡和LabVIEW的马达编码器测试系统(11-06)

- 基于虚拟仪器的网络虚拟实验室构建(11-06)

- 运用LabView控制DS3900串口通信模块(02-02)

- 采用模块化仪器,对新兴音频和视频应用进行测试(02-19)