增量累加ADC以高24位的精确度测量小模拟信号

转换时间。转换时钟可以从内部提供,或者采用外部晶体或硅振荡器。不过,既然数字滤波器不抑制振荡器频率,那么采用内部振荡器是有优势的。

由于数据延迟,当前输出结果落后于输入一个采样周期。凌力尔特公司所有无延迟增量累加(No Latency Delta SigmaTM)转换器都在一个周期内稳定,简化了多路复用应用。

增量累加ADC虽然本质上很简单,但是配置这种ADC却常常是一个复杂的过程,如要写很多指令、平衡输入级的复杂性和选择外部振荡器。凌力尔特公司的增量累加转换器没有校准序列、配置寄存器、滤波器稳定时间和外部振荡器,降低了设计的复杂性。每个转换周期中都执行透明的偏移和满标度自动校准,以确保高准确度,而高准确度则保证能够分辨出1克或0.01度的差别。

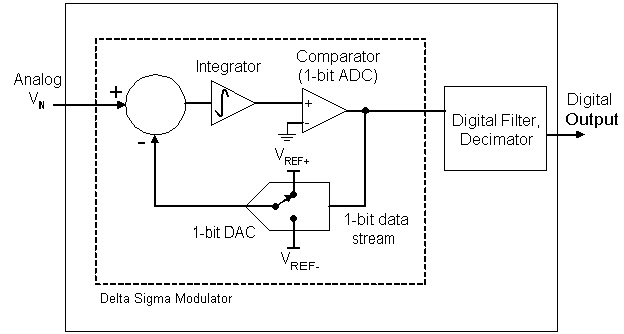

图 1:增量累加 ADC 由执行模数转换的增量累加调制器及其后的数字滤波器和抽取器组成

analog:模拟

integrator:积分器

comparator:比较器

1-bit ADC:1 位 ADC

digital filter:数字滤波器

decimator:抽取器

digital output:数字输出

1-bit DAC:1 位 DAC

1-bit data stream:1位数据流

delta sigma modulator:增量累加调制器

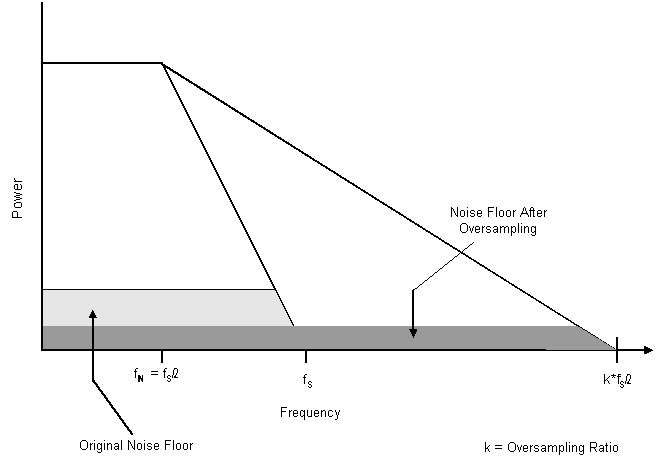

图 2:过采样缩小了所关注频带中的噪声层

power:功率

noise floor after oversampling:过采样后的噪声层

orignal noise floor:最初的噪声层

frequency:频率

oversampling ratio:过采样率

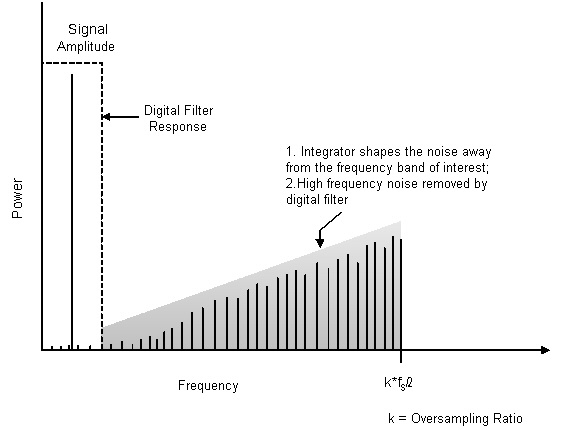

图 3:积分器将噪声强制推移到更高的频率上

Signal Amplitude : 信号幅度

Digital Filter Rsponse : 数字滤波器响应

power:功率

1.积分器将噪声强制推移到所关注的频带之外;

2.数字滤波器滤除高频噪声

frequency:频率

oversampling ratio:过采样率

作者:

凌力尔特公司

产品市场工程师

Steve Logan

ADC 相关文章:

- A/D变换器对频谱仪和信号分析仪动态范围的影响(11-21)

- 一种改善DDS性能的倍频方法 (02-23)

- 利用先进测试平台进行ADSL芯片的关键参数测试(04-29)

- 高输入阻抗的轨至轨测量系统的电路实现(05-04)

- 逻辑分析仪应用于ADC及相关领域(07-13)

- 精确测量ADC驱动电路建立时间(02-24)