测量磁盘驱动器柔性电路的互连阻抗测试

构的阻抗特征可以通过执行虚拟TDR获得。此外,还测量了沿传输线和堆叠变化的阻抗。

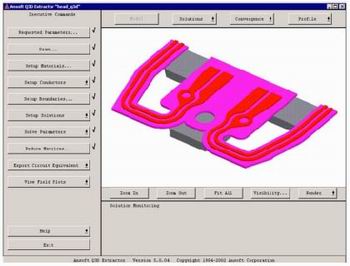

典型的FOS原型的制造和测试周期包括在HGA上制造和装配柔性电路,这一过程需要5到6个星期才能完成。在设计过程中采用 Ansoft公司的 Spicelink技术,所耗时间将会有效地减少到4-5天。此外,在不需要增加与制造和测试相关的时间与成本的基础上,通过迅速进行容差分析,采用 EDA工具能够得到更为鲁棒的设计。

在交付生产前,预测新设计的性能可以确保识别并矫正不需要的电效应。在3M的柔性设计过程中引入Ansoft公司的EDA工具,极大地减少了成本并缩短了上市时间。

参考文献:

1. Howard W. Johnson, Martin Graham. "High Speed Digital Design: A Handbook of Black Magic." Prentice Hall PTR, 1993.

2. Robert Dodsworth, George Hare. "HGA Technology Driver-The Need for Speed." CleanRooms/DataStor Asia, 2001.

3. Eric Jensen, Mike Resso, Dima Smolyansky, Laurie Taira-Griffin. "Improved Method for Characterizing and Modeling Gigabit Flex-Circuit Based Interconnects." DesignCon, 2001.

作者:Chow Wai Kong

Ansoft 公司

Ho Voon Yee

3M亚太公司

- 选择恰当测试平台简化HDMI设备的调试与验证(11-05)

- 利用OTDR快速定位光缆线路故障(02-22)

- 几种常用光纤测试仪器的性能介绍(06-08)

- OTDR光纤测试法的参数设置(01-10)

- 如何选择OTDR光时域反射仪(02-06)

- 正确测量TDR上升时间(01-12)