减少DDR记忆体验负载的探测技术

理 想上,DDR的可测试性应成为最终设计的一部份,以利于在测试台进行系统的验证,因为在整个产品生命周期中的工程设计与委外代工都会增加成本。然而碍于逻 辑分析仪探测点的电气负载与空间需求,这种作法直到今天仍不可行。新的免接头式逻辑分析仪探测技术使DDR可测试性得以结合到产品的最初与最终阶段,对成 本、电路板空间或信号完整性的影响十分有限。

免接头式探测技术

最近,一些逻辑分析仪厂商推出了一种新的"免接头式"(Connector-Less)测试探棒,它们采用压缩互连(compression interconnect)技术,省去了在目标上使用接头的不便。取代接头的是置于代测电路板上的小着陆焊垫(landing pads),测试探棒的电气互连会被压缩到这些焊垫上,以构成电气接点。拿掉占面积的接头,意谓着结合逻辑分析仪可测试性只需要用到最小的空间。此外,不 使用接头也能减少测试探棒的总负载。较低的测试探棒电气负载(< 0.7 pF),表示当连接测试探棒时,信号不会受到电气的干扰。而且,由于代测电路板上面并未留有接头,所以在未连接测试探棒时,只剩下着陆焊垫,而这些焊垫的 负载非常的小(~80fF)。现在,将逻辑分析仪的测试点放入最终的生产设计中已是实际可行的作法。

DDR系统

DDR内存最常见的一种实作方式,就是使用插座式的DIMM或SO-DIMM。工程师将多个184接脚的DIMM并排放置,并且共享内存总线来提高储存容 量。这种实作方式具备了弹性扩充的好处,因而广泛应用于计算机系统中。此种实作方式看似简单,实际上系统工程师必须解决许多问题与限制。

第一个问题是空间。电路板的空间是有限的,因此内存系统的实作应尽可能占用较小的空间。

第二个重要的限制是成本。成本的主要影响在于必须减少代测电路板上的层数。许多DDR系统都是在4层PCB板上实作,而它们只有2个信号层。虽然DDR插座是针对这类路由来做脚位安排,但要容纳DDR系统也需要的各种电路其实是一大挑战。

信号完整性是工程师必须面对的另一个问题。少量的信号与高资料速率,使DDR系统的实作变得非常困难。再加上只有2个路由层及系统必须尽可能缩小的额外限制,造成设计超出边限的情况将会持续出现。

最 后但很重要的一个问题就是可测试性。工程师在面对以上所有的限制之后,系统中通常已经没有太大的空间可以结合可测试性了,然而可测试性却是产品验证与快速 上市的关键。更糟的是,在产品生命周期中经常会变更设计或进行昂贵的工程。当产品在生产过程中有所变更时,必须有一个快速而可靠的方法来验证这些变更是否 改变了设计的原始功能。基于电气负载与空间/路由的需求,直到今天仍无法在生产设计中加入可测试性。现在,免接头式逻辑分析仪探测技术让一切都改观了。

使用免接头式探测技术来执行DDR验证

免接头式逻辑分析仪测试探棒非常适合用于DDR系统的除错,主要的理由包括占位面积小、连接时的负载低、不连接时的负载几乎微不足道、以及flow-through routing(布线穿透)能力。为说明这类探测技术的能力与多元性,当配备如安捷伦科技的Soft Touch等免接头式测试探棒时,可以考虑以下的内存系统。

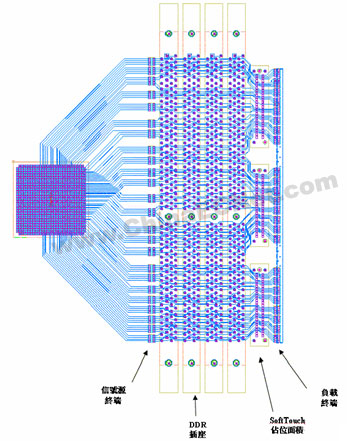

下 图是一个使用4插座、184接脚DIMM的DDR系统之布局范例。这个系统利用位于终端之间的免接头式测试探棒(mid-bus探测)来作2个阻抗匹配。 这个图显示了所有2x信号(资料和stbs)的上方路由,而1x信号(地址和控制)则是在电路板底部以类似的方式传送。每根Soft Touch测试探棒所占的面积包含了34个频道的可测试性。要测试DDR系统中的2x资料,需要3个占位面积。PCB底部包含2个Soft Touch占位面积,可测试所有的1x DDR信号。为了解免接头式测试探棒的能力,必须探讨对系统所造成的额外影响。

图1. DDR系统的Soft Touch探测技术之布局范例(只显示上方的2x数据)

空间的影响

增加免接头式测试探棒的占位面积,会使内存系统所需的空间在X轴多出0.39英吋。换句话说,负载终端电阻的位置必须离最后一个DIMM插座0.39英 吋。如果量测内存系统从最左边驱动器IC所产生的电路板trace到负载终端电阻最右边的相对大小,可以发现使用免接头测试探棒所增加的空间小于10%。

免 接头式测试探棒另一个

DDR 相关文章:

- 可测试高数据速率PCIe2.0系统的分析仪/检测仪(05-18)

- DDR3测试的挑战及解决方法(05-09)

- 泰克的DDR测试和验证解决方案系列增加两项新功能(11-13)

- DDR-1500/DSC-2200在高性能测试测量中的应用(05-03)

- DDR测试技术和工具是否跟上了时代步伐?(03-02)

- 利用新一代虚拟探测功能实现DDR等信号去嵌测试(01-09)