在SOPC上实现的波形发生器

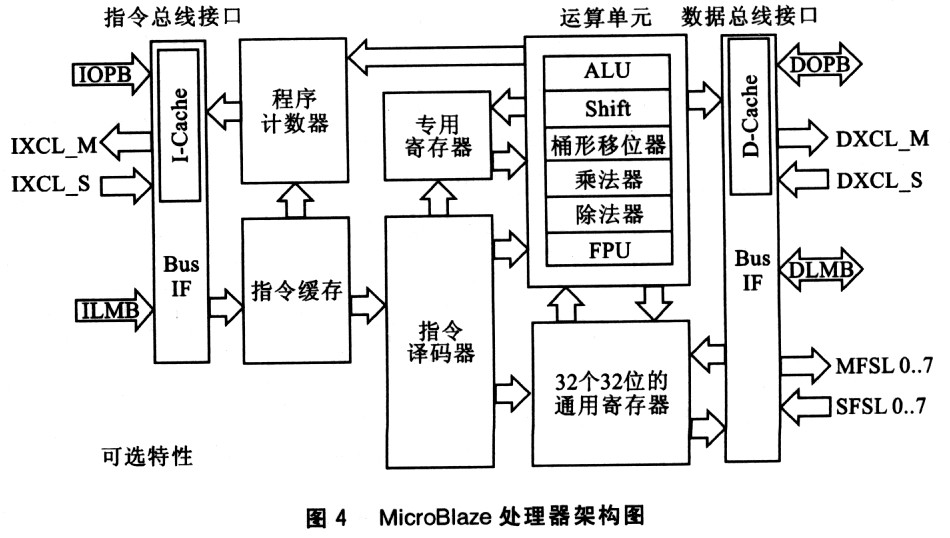

MieroBlaze是Xilinx提供的32位微处理器IP核,是哈佛结构的RISC微处理器,有较高的性能。它可以在性价比很高的 SpartanIII系列FPGA上实现。EDK为其提供了MB-GCC,支持C及C++语言。MicroBlaze架构如图4所示。

该处理器含有32个32位的通用寄存器,2个专用寄存器,独立的32位数据和指令总线,并与IBM的OPB总线完全兼容,具有32位的指令宽度支持三个操作数和两种寻址模式,以及可选的硬件乘除法及浮点运算单元。

2.2 DDS IP的实现

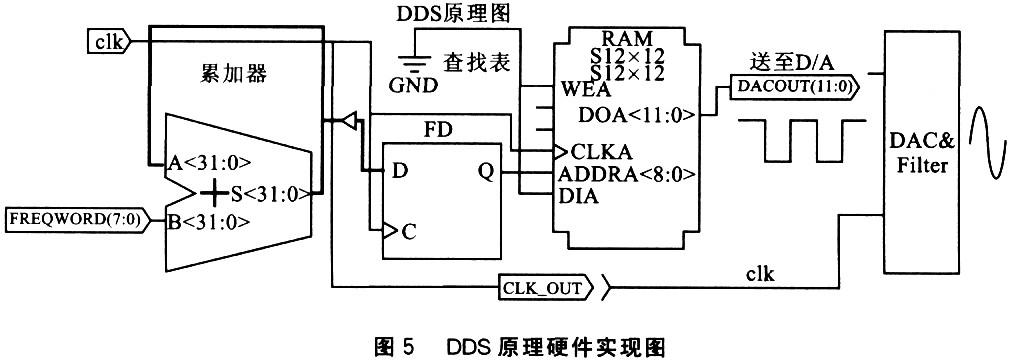

数字直接频率合成技术(Direct Digital Frequemy Syn-thesls,简称DDS或DDFS)的基本原理是利用采样定理,通过查表法产生波形,其基本电路原理如图5所示。

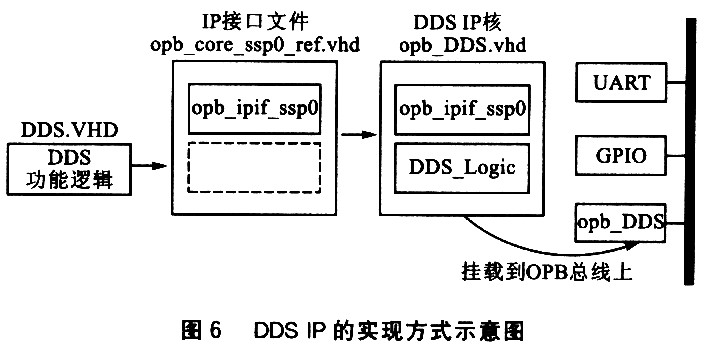

DDS的频率及步进容易控制,且合成的频率取决于累加器及查找表的速度,采用FPGA可以很好的发挥这项优势,获得精细的步进及宽频带。使用HDL硬件描 述语言,可以很方便的描述出DDS的FPGA硬件实例。在基本的DDS模块上,添加相应的控制寄存器,通过向不同的寄存器内写人相应的控制字,实现频率以 及幅度的可控性。最后通过IBM CoreConnect技术,在DDS模块外面添加总线接口,作为自定义IP,成功地将其挂载到系统总线上,便可以方便的对其进行读写操作,实现DDS模 块与MicroBlaze的通信。图6是从用户逻辑到成为符合IBM CoreCormect技术规范的DDS IP的实现过程。

DDS的VHDL代码作为子模块与opb_core_ssp0_ref.vhd模块共同构成opb_DDS IP Core,其中ipif(IP InterFace)符合IBM CoreConnect规范,负责DDS逻辑与OPB总线之间的通信。在EDK中,通过Create/ImpottIP工具把opb_DDS添加到系统 中,并为其分配地址,建立端口连接,之后就可以使用该IP了。DDS IP配合控制程序可产生各种波形,并对频率、幅度进行精确的控制。

2.3 其余部分

系统所需要的LCD显示、DAC控制等模块,均通过与生成DDS IP相同的方式,编写为符合IBM CoreConnect总线规范的IP,以供使用。

在硬件系统构建完毕之后,使用Platgen工具生成网表文件和Bitgen工具生成相应的硬件配置文件。若将工程导入到ISE软件中,可以进行优化设 置,还可以将工程导人到其他的综合工具如Synplify Pro进行实现。IP核的编写是在ISE中完成的。无论对于整个系统还是一个单独的IP,都可以利用Modelsim工具进行行为及时序仿真。最后,为此 系统描写XBD(Xilinx Board Description)板级描述文件,通过此文件,EDK可以通过BSB(Base System Builder)模式自动生成基本的硬件系统,并对所添加的端口进行约束,这样可以实现资源的继承性使用。

3 软件系统的实现

EDK提供了免费的GNU C Compiler,可以支持标准C。同时,EDK为多种IP以API的形式提供了驱动函数,有利于程序的开发。XPS所集成的软件工程管理工具允许在一个 硬件平台上同时开发多个软件工程。完成软件代码的编写后,使用EDK集成的XMD和GDB调试器对代码进行仿真和调试,也可以配合ChipScope(片 内逻辑分析仪)进行硬件及软件的协同调试。XMD通过MDM模块和JTAG口连接目标板上的CPU,GDB可以对程序进行单步调试或断点设置。针对本设计 及应用,编写了系统控制及晶显示程序。程序编译后生成为elf文件,通过Update bitstream工具把程序同硬件配置文件合成为Download.bit文件,把此文件下载到目标板后,FPGA首先根据硬件配置信息建立硬件系统, 并把程序代码映射到片内BRAM中,最后启动.MicroBlaze,运行程序。

4 总结

本系统基于FPGA,以MicroBlaze为核心,加入具有良好特性的DDSIP,并辅以必要的外围电路,构成了高度集成化的系统。另外,SoPC系统 的柔性配置,使得可以基于此系统扩展片外存储器,并可以实现RTOS操作系统的移植,以实现更丰富的功能和完成更复杂的任务。

- 基于DDS的多功能中频信号源的设计及其在雷达系统中的应用(11-03)

- 基于DSP和DDS的商品防窃监视器扫频信号源(11-03)

- DDS器件AD9858及其在雷达信号源中的应用(11-03)

- 高性能DDS芯片AD9954及其应用(11-03)

- 直接数字合成电路在雷达信号设计中的应用(11-03)

- ADI集成DAC的数字频率合成器时钟速度提高到两倍(11-12)