直接数字合成电路在雷达信号设计中的应用

随着科学技术的发展,雷达对信号的要求越来越高。雷达信号必须具有频率捷变、波形参数捷变和自适应跳频的能力。传统的模拟方法只能产生单一的雷达信号,而 利用直接数字合成(DDS)是解决这一问题的最好途径。专用DDS电路AD9854可以产生点频、线性调频、FSK、BPSK等各种信号形式,其幅度和相 位一致性好,还有电路控制简单、方便灵活、可靠性高等优点。

2 AD9854 的结构特点

AD9854是Analog Devices公司推出的专用DDS电路,主要特点如下:

(1)工作速度高达300MHz,单电源3.3V供电,最大功耗1.2W(利用节能方式降低),窄带杂散83dB,宽带56dB,宽带杂散随着频率的提高降至48dB。

(2)包含两个12位高速、高性能D/A转换器和比较器,还有两个48位可编程频率寄存器、两个14位可编程相位寄存器、12位幅度调制器和可编程的波形开关键以及时钟可编程。

3 基于AD9854 的原理框图

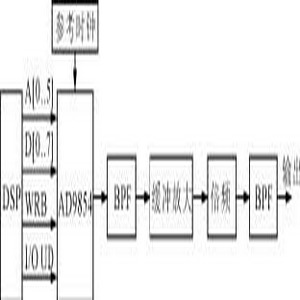

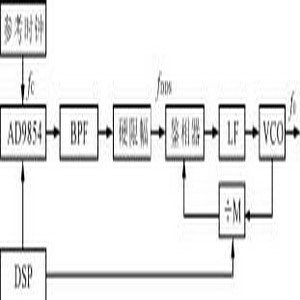

一般DDS输出频率范围从直流到40%fC,相对带宽很宽,但目前时钟频率fC较低,使DDS直接输出频率上限较低,实际工作频带较窄。为了扩展带宽,提 高DDS频率上限,我们常采用倍频、数字上变频、混频等方法。下面主要介绍用DDS加其他合成技术产生宽带雷达信号的两种方案。分别如图1和图2所示。

图1 DDS+倍频扩展频带方案的原理框图

图2 DDS+PLL 扩展频带方案的原理框图

方案1采用开环系统结构,使得该系统具有很快的频率捷变速度,结构简单,低杂散、低谐波性能容易实现。方案1的相位噪声和杂散性能主要受DDS特性的影 响,表现在相位截断误差、幅度量化误差以及DAC非线性引起的误差。 方案2除了受DDS特性的影响,还受LF、VCO的影响。方案2采用闭环系统结构,故频率转换时间较长,由于采用了锁相倍频环,具有很高的工作频率、宽的 频带及纯的频谱。 由于采用了专用DDS电路,故两者都具有频率稳定度高、可编程控制等优点。

4 AD9854 的软件编程

AD9854有5种可编程的工作模式,可以在控制寄存器中设置,分别为:

( 1) Single- Tone ( Mode 000) ;

( 2) Unramped FSK ( Mode 001) ;

( 3) Ramp FSK ( Mode 010) ;

( 4) Chirp ( Mode 011) ;

( 5) BPSK ( Mode 100) 。

下面就(4)、(5)两种工作模式的软件编程作一详细介绍。

4.1 FMChirp 的基本编程步骤

将1个初始频率f0写进FTW1中(FrequencyTuneWord1,并行寄存器地址04H-09H),FTW1由FTW1=(期望输出频率×2) /系统时钟确定,其中N为相位累加器分辨率。 Frequency Word,并行寄存器地址10H-15H)。 Rate Clock,并行寄存器地址1AH-1CH)。

当编程完成后,触发引脚20上的I/O更新脉冲。

例程1:(DSP 采用Analog Devices公司的AD21065L)

* ** * 长 脉冲 纯 线 性调 频 * ** * *

chirp_100: M0=0x04 ;

f0=16MHz R8=0x14 DM( M0,I0) =R8 M0=0x1E ;

SYSTEM CLK=40M× 5=

DM( M0,I0) =R8

M0=0x05

R8=0x80

DM( M0,I0) =R8

M0=0x1F ; 工 作 模 式 =011

R8=0x86

DM( M0,I0) =R8

M0=0x1C ; RAMP CLK=0.1μ s

R8=0x13;

DM( M0,I0) =R8

M0=0x11 ; Delta Frequency=8kHz

R8=0x01

DM( M0,I0) =R8

M0=0x12

R8=0xDC;

DM( M0,I0) =R8

M0=0x13

R8=0xE0 ;

200MHzR8=0x45DM( M0,I0) =R8M0=0x1F ;

acc2 置 1R8=0xc6DM( M0,I0) =R8BIT SET ASTAT ASTAT_FLG2;

产 生 一个 UPDATE CLKNOP BIT CLR ASTAT ASTAT_FLG2

Chirp_100_end BIT SET MODE1 IRPTEN RTI NOP NOP

4.2 BPSK 的基本编程步骤

将载频f0写进FrequencyTuningWord1。 Adjust Register 1和2中。 连接BPSK数据源到引脚29。 当编程完成后,触发引脚20上的I/O更新脉冲。

例程2:(DSP采用AnalogDevices公司的AD21065L)

*****二相码子程序*****

bpsk_100: M0=0x04 ;F0=20MHz R8=0x19 DM( M0,I0) =R8 M0=0x05 R8=0x80 DM( M0,I0) =R8 M0=0x1E ;SYSTEM CLK=40M× 5=

:200MHzR8=0x45DM( M0,I0) =R8M0=0x1F ;工 作 模 式 =100

R8=0x08 DM( M0,I0) =R8 M0=0x1F ;acc2 置 1R8=0xc6 DM( M0,I0) =R8 M0=0x00 ;初 相 为 90°R8=0x10 DM( M0,I0) =R8 M0=0x02 ;初 相 为 270°R8=0x30 DM( M0,I0) =R8 BIT SET ASTAT ASTAT_FLG2

;产 生 一 个 UPDATE CLKNOP BIT CLR ASTAT ASTAT_FLG2

bpsk_100_end: BIT SET MODE1 IRPTEN RTI

NOP NOP

5 结 论

由于采用全数字结构,DDS具有极高的频率分辨率(达Hz、mHz)、极短的频率转换时间(可达ns量级)、输出频率相对带宽很宽、具有任意波形输出能力 和程控灵活等特点,是传统的模拟信号产生技术无可比拟的。但DDS是1种新技术,目前输出频率还不高,它的全数字结构,又带来了杂散电平和谐波电平高的缺 陷。

DDS 相关文章:

- 基于DDS的多功能中频信号源的设计及其在雷达系统中的应用(11-03)

- 基于DSP和DDS的商品防窃监视器扫频信号源(11-03)

- DDS器件AD9858及其在雷达信号源中的应用(11-03)

- 高性能DDS芯片AD9954及其应用(11-03)

- 在SOPC上实现的波形发生器(11-03)

- ADI集成DAC的数字频率合成器时钟速度提高到两倍(11-12)