JPEG2000编码器IP核设计,包括具体算法与结构

经过这段时间的调用,阅读文献,决定采用"High-Speed VLSI Implementation of 2-D Discrete Wavelet Transform",Chao Cheng and Keshab K. Parhi文中描述的算法。该算法具有对称统一的结构,可以方便的均衡硬件使用和分解效率,通过选取适当的并行级别,我们可以得到满足需要的DWT分解元件。具体介绍见下面2部分。

5.3.1 基于并行FIR滤波器的1-D DWT结构

为了便于说明问题,假设滤波器的长度为4,初始图像大小为NxN=8x8。低通滤波器:H={a,b,c,d}; 高通滤波器:G={e,f,g,h};原始图像

首先在行方向通过低通滤波器,并进行下抽样,得到(2)式

从(2)式中可以简化得到(2a)式

该式可以转换成矩阵形式,并可变换为(2b)式

从(2b)式,我们看到1-D DWT(2a)已经转换成2个只有原始滤波器一半长度的FIR滤波器。

当对(2b)式使用2输入FIR结构,对于 的计算只需要2个时钟周期,首先得到

的计算只需要2个时钟周期,首先得到 ,接着得到

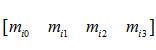

,接着得到 。对(1)式的行滤波可以用如图1所示的滤波器结构实现。

。对(1)式的行滤波可以用如图1所示的滤波器结构实现。

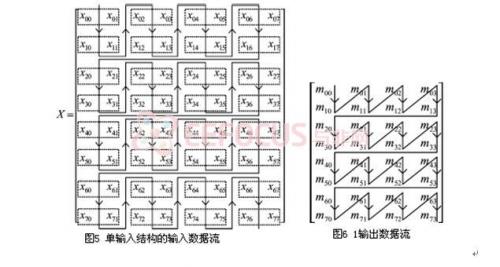

以上结构所需要的硬件资源为3个乘法器,4个加法器和1个延时元件。输入数据流见图2所示,对应的输出数据流见图3所示(即mij输出)

从数据流中可以看出,图1(b)中的每个D要用4D代替。

5.3.2 2-D DWT结构(N2/2结构)

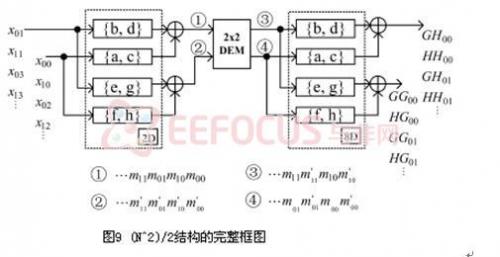

使用1输入的FIR滤波器代替之前的2输入滤波器我们可以得到N2/2速率的结构。其对应的数据流如图5和图6所示。进一步,可以进行列方向的分解,具体过程如同行方向分解,如图7所示。但若将行和列部分同步起来,还存在一个问题,可以从数据流中看出,例如计算出m00和m10需要2个周期,而列分解需同时处理m00和m10。要在N2/2个时钟周期内完成该分辨率级分解,还需要一个DEM元件,即Delay Element Matrix,其内部结构如图8。

最终我们得到了进行一级分解的完整结构如图9

若进行多级小波分解,还需要缓存HH子带的数据,并进行同样过程的处理。

利用此算法,我们可以轻易的扩展到JPEG2000编码器中所使用的9/7和5/3小波的硬件结构,该结构在计算速率上有着很大的优势,同时也会在资源使用上耗费更多的资源,但硬件资源的耗费可以控制在一个合理的范围内。一个9/7小波算法实现的技术参数比较见下表:

- 如何通过开源API进行DSP视频处理(02-15)

- 一种输出格式可控的多码率LDPC编码器实现(11-06)

- 基于DM365的视频编码器的硬件设计(10-15)

- 音视频SoC测试要求与应用介绍(07-20)

- H.264在ADSP-BF561上的实现与优化(05-27)

- 一种简单串行鼠标控制的单片机实现(03-19)