基于VHDL的洗衣机控制器的设计

2.3控制模块设计

控制模块是洗衣机控制器的核心模块,它根据按键选择模块输入的各种控制信息和计时模块输入的计时信息控制洗衣4种状态的转换和电机转速,并输出当前洗衣状态、电机转速,以及剩余时间。

洗衣四种状态的转换可以方便对由状态机实现。状态机是一种输出由当前状态和当前输入决定的时序电路,它通常可以用状态转换图表示。使用VHDL设计状态机不必知道电路的具体实现细节,只需在逻辑上加以描述,因此采用状态机实现控制模块是一种非常方便的方法。

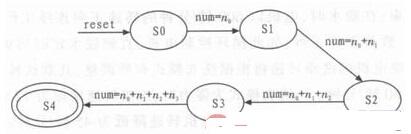

状态机的用VHDL实现有通用格式,它包含两个个进程:状态机状态转换进程Change_State和状态机输出进程Output_Process.其中状态转换进程由状态转换图决定,洗衣机的状态转换图如图2所示,S0、S1、S2、S3、S4分别为进水、洗涤、漂洗、脱水以及结束状态,n0、n1、n2、n3分别表示由按键选择模块输出的进水、洗涤、漂洗与脱水时间,num为计数模块输出的洗衣机运行时间,reset为洗衣机启动信号。当洗衣机启动时,即reset按键拨动,进入S0状态,开始进水;当洗衣机运行时间num=n0时,进水完成,状态转为S1,开始洗涤;当洗衣机运行时间num=n0+n1时,洗涤完成,状态转为S2,开始漂洗;当洗衣机运行时间num=n0+n1+n2时,漂洗完成,状态转为S3,开始脱水;当洗衣机运行时间num=n0+n1+n2+n3时,脱水完成,状态转为结束状态S4,洗衣停止。

图2 洗衣机状态转换图

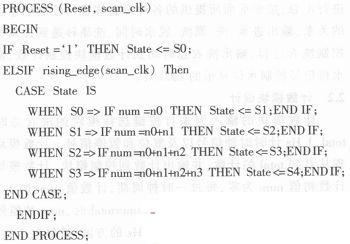

状态转换进程的VHDL代码如下:

当reset=1时,启动进程,当前状态state置S0.每当扫描时钟scan_clk为上升沿时,启动进程,根据当前状态state和洗衣机运行时间num,按照状态转换图决定新的当前状态。

输出进程通过输出4种洗衣状态信号控制4个LED灯当明灭来显示当前洗衣状态。输出进程通过输出进水信号控制进水。当洗衣为进水状态时,若暂停信号为0,则输出进水信号为1,开始进水;若暂停信号为1,输出进水信号为0,暂停进水。而当洗衣为其他状态时,输出进水信号始终为0,停止进水。输出进程通过输出电机控制信号控制电机运行。根据洗涤电机的逻辑控制过程,当洗衣状态为进水时,输出电机控制信号为零电平,表示电机暂停;当洗衣状态为洗涤和漂洗时,输出电机控制信号为频率为洗涤转速(默认60转/分钟,即1Hz)的方波持续5秒(默认时输出1 Hz的方波5个),然后高电平持续1秒(控制电机极性转向);洗衣状态为脱水时,输出电机控制信号为频率为脱水转速(600转/分钟,即10 Hz)的方波持续5秒(默认状态下,输出10 Hz的方波50个),然后零电平持续1秒(控制电机暂停)。输出进程根据当前状态和洗衣机运行时间输出当前状态剩余时间到显示模块。例如,当洗衣为洗涤状态时,输出剩余时间为n0+n1-num.

2.4显示模块设计

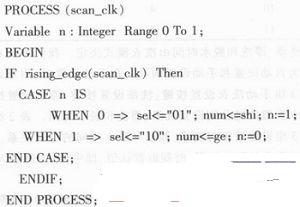

本模块用于在7段数码管上显示当前状态剩余时间,其输入为控制模块输出的当前状态剩余时间和扫描时钟。首先,将输入的剩余时间由秒转换为分钟(四舍五入);然后进行分位,分为个位ge和十位shi(显然剩余时间不超过100分钟,最多2位);最后通过动态扫描在2个共阴极的七段数码上交替显示个位数字和十位数字。当交替频率高于28 Hz时,由于人眼的视觉残留效果,这2位数字看上去是同时显示在2个七段数码管上。动态扫描进程的VHDL代码如下:

3结束语

我们在QuartusⅡ软件开发平台上,基于模块化的设计思想,使用VHDL语言完成洗衣机控制器设计、编译和仿真,并下载到FPGA硬件实验箱上进行测试。仿真波形和测试结果表明该洗衣机能正确实现各种设计功能,该设计方案切实可行。

- 用VHDL语言在CPLD上实现串行通信(10-13)

- 基于Max+Plus II和VHDL的电子密码锁设计(10-15)

- 数字电视机顶盒设计方案、技术文献集锦(02-25)

- 基于打印机的设计方案及实际应用案例汇总(03-03)

- 基于FPGA 的高阶全数字锁相环的设计与实现(07-18)

- 基于cyclone EP1C6 的LED大屏设计方案(07-22)