音视频SoC测试要求与应用介绍

频DAC:2个用于S-Video、1个用于复合输出、3个用于RGB。

虽然数字视频标准最高要求的接口速度为74MHz,但测试DAC性能要求的模拟带宽约为8MHz,分辨率10至12位。单个视频DAC的典型测试项目包括积分非线性(INL)、微分非线性(DNL)以及SND测量。而HDTV系统的图形质量是由DAC输出的相对精度决定的,须对输出增益和相位匹配作附加测试。内置数字视频器件的总测试时间与测试可提供的并行数字化仪的数量直接相关。待测视频DAC的数量通常在6个以上,由于缺乏测试仪资源,建立一套串行化测试方案是必不可少的。并行测试方案

虽然降低总COT受多个变数的影响,但实施多点测试和并行测试来改进吞吐率无疑是主要方法。最新一代ATE系统采用多端口体系结构,支持成组的和待测器件功能相匹配的测试仪资源结构。

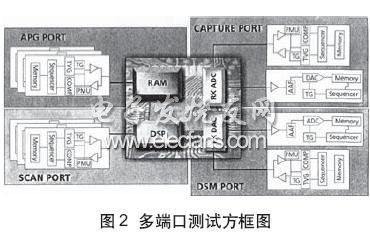

实现上述目标的两个主要功能是每端口定时发生器和每端口序列发生器,前者与测试芯核的频率相匹配;后者可工作在不同测试模式并自动地执行序列指令。每引脚多端口方案比上述方案更进一步,将ATE系统的数字和模拟两种资源的粒度细分至每个引脚。测试典型SoC的必备的资源结构实例包括:用作通信处理器的DSP、存储器,以及与模拟IF或RF前端接口的ADC和DAC。在本场合,数字引脚配置成扫描模式,用来测试DSP芯核(见图2)。

ADC块需要任意波形发生器(Arb)和数字通道,数字通道处于捕获模式来采集与分析ADC的输出。DAC则需要多个数字通道组成的端口,用数字源存储器(DSM)或波形存储器段以及波形数字化仪来测试。每个端口能自动地工作在不同的测试频率,执行不同的序列指令。

由于测试系统已在每个引脚基础上进行分段,通过复制测试矢量的映象和每测试点使用的引脚上序列,应用软件能自动地管理绝大部分多测试点的控制。

并发测试是多端口测试的扩充,让这些芯核并行地进行测试。当然,器件中每个芯核应是ATE系统可独立地访问和控制的,能独立工作的。将每个器件芯核串行测试的纯序列流修改为多个器件芯核并行测试的序列流,能大大减少测试执行时间(图3)。

在大规模器件(如无线基带SoC处理器)中,有无数个模拟芯核,并行地测试这些芯核需要大量的模拟资源。若按4个测试点,全并行、并发测试式计算,需提供28个数字化仪,这在当前的ATE系统中还难以实现。

一种新型模块体系结构

测试当前消费品器件中使用的各种模拟芯核,需要高度并行,低开销的解决方案。若在每个模块中组合几个模块功能,能相应地减少每个模拟模块的占用空间,这样,就有更多的空间留给必需的数字模块。一个内置8个独立Arb或数字化仪单元的模块具有灵活地配置的优点:或只用作数字化仪单元,或是数字化义与Arb单元的组合。

降低消费类器件测试的COT不仅要解决ATE测试系统的并行测试方案,还要减少并行测试带来的ATE开销。多芯核是当前SoC消费类器件的主要特征,在对ATE硬件进行体系结构改进时同样要考虑上面两个因素,这样才能得到最佳的测试解决方案。

- LCoS(硅基液晶)显示屏设计与应用(08-27)

- 系统级芯片发展之路依然任重道远!(11-13)

- 在SoC中集成FlexRay网络控制器的设计策略(01-08)

- 用于便携式多媒体SoC的视频处理方案 (02-09)

- H.264音视频编解码SoC芯片Hi3510的原理和应用 (02-22)

- 数字视频系统设计中的集成新概念 (07-22)