基于CCD星载相机图像采集电路设计与实现

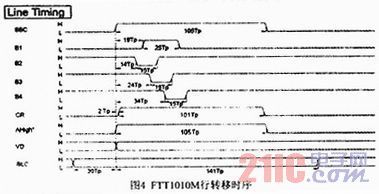

传感器无像素电荷输出。FTT1010M行转移时序如图4所示。

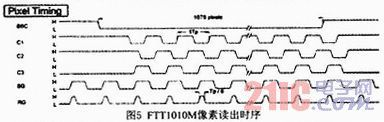

在行正程阶段,SSC为低电平,行转移信号B1、B2、B3、B4不发生变化,水平移位寄存器中的像素电荷在像素转移信号C1、C2、C3的控制下逐次经过输出放大器输出,每输出一行信号后,进行一次行转移。FTT1010M像素读出时序如图5所示。

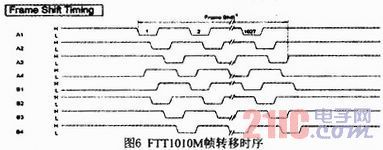

在转移阶段,帧转移控制信号A1、A2、A3、A4与行转移控制信号B1、B2、B3、B4同时作用,交叠变化,将感光区积累的电荷逐行转移到存储区,而在这段时问内像素转移信号C1、C2、C3不起作用,不向外输出电荷。完成整个转移阶段后,又再次进入感光阶段,如此循环往复来保证图像传感器的工作。FTT1010M帧转移时序如图6所示。

3 CCD偏置电压电路

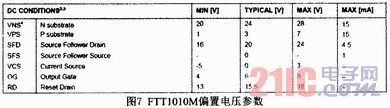

若要使CCD图像传感器芯片正常工作,就需要向CCD提供使其正常工作所需的偏置电压。FTT1010M所需的偏置电压有VNS、VPS、SFD、RD、OG等,它们的参数如图7所示。设计时,作者采用的电压转换方案是使用低纹波的转换芯片搭配转换电路,VNS(24V)由外接28V电压通过DC/DC变换器LT3060得出,SFD由VNS通过电平转换电路得出,VPS、RD与OG由SFD的分压引出。

4 CCD驱动电路

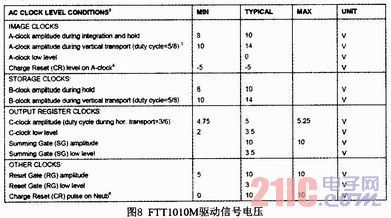

FTT1010M工作时所需的各种脉冲信号的电压如图8所示。

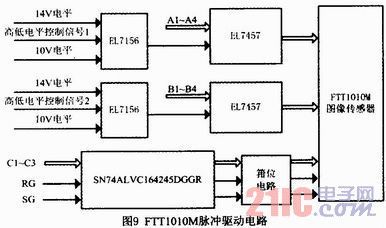

A、B驱动时钟的低位电平为0V,由图8可以看到,在感光阶段,A、B驱动时钟的高位电平为+10V,转移阶段时,A、B驱动时钟的高位电平为+14V。这里我采用EL7156来实现高位电平之间的转换,采用EL7457来实现低位到高位电平的转换。水平读出时钟C需要的低电平不是0V而是3.5V,高电平为8.5V,而FPGA给出的时钟脉冲是低电平为零,高电平为3.3V的脉冲。因此,需要将FPGA产生的时钟通过驱动芯片SN74ALVC164245DGGR进行驱动,使时钟C的幅值达到5V,然后再通过箝位电路的耦合作用来提高脉冲电平,把脉冲提到需要的幅度。SG、RG的产生过程与时钟C的产生过程类似,不同的是其幅值要求为10V。

各种驱动脉冲信号的幅度调整电路如图9所示。

5 CCD输出保护电路

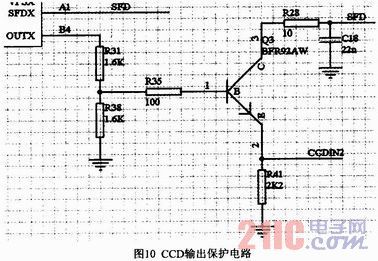

CCD传感器是一种MOS器件,操作不当就很容易受到静电损坏,在电路设计时应在其外围电路加上箝位、限流电路以确保加在CCD上的每一个偏置电压和驱动脉冲受到电流保护,在输入到FTT1010M之前应该通过一个电容来解耦,并且这些解耦电容应该与图像传感器引脚越近越好。FT T1010M的输出端为开源输出,应该在其输出端上接一个电流源做负载,或接一个电阻到地上。在输出上加一个射极跟随的高频三极管,以阻止输出因容性负载而引起的带宽限制。除此以外,射极跟随器加在输出端还可以防止示波器的探头对FTT1010M造成的静电损坏。CCD输出保护电路如图10所示。

6 CCD输出预处理电路

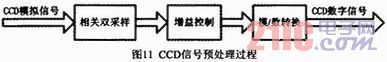

在CCD成像系统中,噪声是限制有效分辨率的最主要因素。CCD输出的信号是具有各种噪声的模拟信号,必须经过预处理,尽可能地消除噪声和各种干扰才能给后续电路使用。为了便于计算机处理,还需要对CCD输出的信号进行A/D转换。预处理过程大体如图11所示。

根据预处理的要求,我们选用了一个高集成度的CCD信号处理专用芯片AD9978,它具有双通道输出能力,且具有14位的A/D转换精度,转换频率可达65MHz,其内部集成了相关双采样、可变增益控制、黑电平箝位电路以及高精度时序产生系统。我们使用相关双采样处理单元,通过两次采样消除不希望的噪声分量,第一次采样位于复位周期结束后,第二次采样位于信号的信息段,两次采样的差就是不含噪声的信号。随后,为了适应不同亮度的目标,防止CCD信号过弱或饱和,我们使用其内的增益控制处理单元来控制信号的增益,最后再通过A/D转换送给后面的可编程逻辑单元进行处理。设计时还要注意使其转换速率与CCD输出像素时钟保持一致。

7 结束语

本文阐述了星载CCD相机图像采集电路的设计与实现,经项目验证表明这些设计能很好地为CCD提供各类偏置电压、驱动脉冲以及电路保护等,它们确保了CCD图像传感器的图像质量,使得CCD相机成像系统具有高性能和高可靠性,具有极高的应用价值。

- TI手提多媒体设备解决方案(09-23)

- 线阵CCD图像传感器驱动电路的设计 (01-02)

- 采用硅存储器的双摄像头式运动型摄像机 (02-02)

- 用摄像手机拍出优质影像基本要素(02-15)

- 数码相机的CCD前端系统方案 (03-07)

- 基于XRD4460的CCD视频信号处理电路的设计(04-15)