DDR存储器电气特性验证

时间:01-20

来源:中电网

点击:

DDR分析软件

泰克实时示波器中的选件DDRA(DPO的泰克实时示波器/DSA70000系列,MSO70000系列,DPO7000系列)是一个软件工具,用于DDR设备测试设置和自动化测试。DDRA提供的符合JEDEC规范的广大的测量设置,但对于非标准设备或系统工程,用户也可以选择自定义多个设置完成测量任务。目前此软件选件支持六种不同的DDR技术:DDR、DDR2、DDR3、LPDDR、LPDDR2和GDDR3。

选件DDRA连同泰克示波器上的另外两个软件:高级搜索&标记(选件ASM,上面已描述)和DPOJET抖动和眼图分析工具,这三个工具结合在一起使用,建立了一个强大、灵活且易使用的DDR测试和调试套件。

DDRA菜单界面有五个步骤,这五个步骤通过选择过程引导用户。在这里,用户选择DDR类型进行测试(DDR、DDR2等)和存储器的速度等级。这个例子中,下拉选择框显示了覆盖所有的DDR标准测试,也可以对速率达到1600MT/s的DDR3进行测试。除了默认选择,用户可以输入用户自定义速度设置,使得软件容易适应未来技术发展。一旦DDR类型和数据速率被选中,DDRA自动配置用于测量正确电压参考。这里会再次出现"用户定义"设置,允许用户不用JEDEC的默认值和输入用户自定义的Vdd和Vref值(如果需要)。

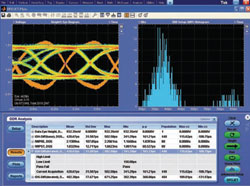

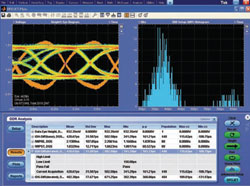

图5 DDRA结果界面显示了两个结果图

第2步允许用户选择执行哪个测量。可用的测量通过下拉菜单选择,这些选项根据信号和探测连接。例如,时钟的测量都归入一个"时钟"下拉菜单中。读测量、写测量和地址/命令测量都被分到各自的下拉菜单。

DDRA菜单界面的步骤3、4和5将引导用户对所需的信号进行探测,并提供自定义或调整参数的设置(如测量参考电平)。

一旦设置完成,用户选择运行<Run>或<Single>),示波器将采集感兴趣的信号,识别和标记数据突发(如果需要)。使用默认的记录长度,示波器通常会采集大约1000UI时间间隔,对采集波形的所有的有效边缘进行测量。软件会自动生成眼图、DQ和DQS重叠显示。在DDRA"结果"面板中显示所有测量结果的统计值、指标极限值、合格/不合格结果和其他数据。还可以生成打印报告,也可以选择保存波形数据进行测量。

数字和模拟联合观测

如前所述,有很多方法去探测DDR信号,从转接内插板到焊接探头的前端。首先需要监测多路数字信号,然后发现信号完整性问题,再增加一个探头查看其模拟信号的波形,这就是所谓的"双探测",这是一个常见的调试方法。这种探测方法会影响被测信号的阻抗,同时使用两个探头会增加信号的负载效应,使信号的上升时间和下降时间、幅度和噪声性能变差。

图6 iCapture结构

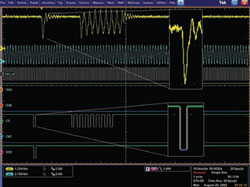

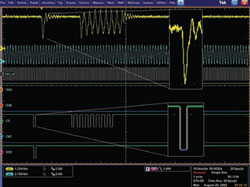

图7 iCapture显示了芯片选择线的模拟和数字联合观测

MSO70000的iCapture功能可以看到时间相关的数字和模拟信号,避免了双探头探测的额外负载电容和建立时间。16个数字通道中的任一通道的信号可以切换到示波器的模拟信号采集来观测,从而提供一个时域相关的数字和模拟信号同时观测。图7显示了验证GDDR5的设计中片选线的一个简单例子。在采集数字信号时,这可以帮助确保正确的逻辑门限电平,或验证信号完整性更准确。

总结

在本应用文章中,描述了与DDR相关的许多测试挑战,并提出了验证和调试存储器设计的工具。关于DDR测试的更多细节,请访问JEDEC的网站http://www.jedec.org/或http://www.memforum.org/index.asp,可以找到详细的DDR规范、白皮书,和其他辅助材料,也可以登录www.tektronix.com/memory,查找关于DDR测试的更多信息。

编辑:吕勇

泰克实时示波器中的选件DDRA(DPO的泰克实时示波器/DSA70000系列,MSO70000系列,DPO7000系列)是一个软件工具,用于DDR设备测试设置和自动化测试。DDRA提供的符合JEDEC规范的广大的测量设置,但对于非标准设备或系统工程,用户也可以选择自定义多个设置完成测量任务。目前此软件选件支持六种不同的DDR技术:DDR、DDR2、DDR3、LPDDR、LPDDR2和GDDR3。

选件DDRA连同泰克示波器上的另外两个软件:高级搜索&标记(选件ASM,上面已描述)和DPOJET抖动和眼图分析工具,这三个工具结合在一起使用,建立了一个强大、灵活且易使用的DDR测试和调试套件。

DDRA菜单界面有五个步骤,这五个步骤通过选择过程引导用户。在这里,用户选择DDR类型进行测试(DDR、DDR2等)和存储器的速度等级。这个例子中,下拉选择框显示了覆盖所有的DDR标准测试,也可以对速率达到1600MT/s的DDR3进行测试。除了默认选择,用户可以输入用户自定义速度设置,使得软件容易适应未来技术发展。一旦DDR类型和数据速率被选中,DDRA自动配置用于测量正确电压参考。这里会再次出现"用户定义"设置,允许用户不用JEDEC的默认值和输入用户自定义的Vdd和Vref值(如果需要)。

图5 DDRA结果界面显示了两个结果图

第2步允许用户选择执行哪个测量。可用的测量通过下拉菜单选择,这些选项根据信号和探测连接。例如,时钟的测量都归入一个"时钟"下拉菜单中。读测量、写测量和地址/命令测量都被分到各自的下拉菜单。

DDRA菜单界面的步骤3、4和5将引导用户对所需的信号进行探测,并提供自定义或调整参数的设置(如测量参考电平)。

一旦设置完成,用户选择运行<Run>或<Single>),示波器将采集感兴趣的信号,识别和标记数据突发(如果需要)。使用默认的记录长度,示波器通常会采集大约1000UI时间间隔,对采集波形的所有的有效边缘进行测量。软件会自动生成眼图、DQ和DQS重叠显示。在DDRA"结果"面板中显示所有测量结果的统计值、指标极限值、合格/不合格结果和其他数据。还可以生成打印报告,也可以选择保存波形数据进行测量。

数字和模拟联合观测

如前所述,有很多方法去探测DDR信号,从转接内插板到焊接探头的前端。首先需要监测多路数字信号,然后发现信号完整性问题,再增加一个探头查看其模拟信号的波形,这就是所谓的"双探测",这是一个常见的调试方法。这种探测方法会影响被测信号的阻抗,同时使用两个探头会增加信号的负载效应,使信号的上升时间和下降时间、幅度和噪声性能变差。

图6 iCapture结构

图7 iCapture显示了芯片选择线的模拟和数字联合观测

MSO70000的iCapture功能可以看到时间相关的数字和模拟信号,避免了双探头探测的额外负载电容和建立时间。16个数字通道中的任一通道的信号可以切换到示波器的模拟信号采集来观测,从而提供一个时域相关的数字和模拟信号同时观测。图7显示了验证GDDR5的设计中片选线的一个简单例子。在采集数字信号时,这可以帮助确保正确的逻辑门限电平,或验证信号完整性更准确。

总结

在本应用文章中,描述了与DDR相关的许多测试挑战,并提出了验证和调试存储器设计的工具。关于DDR测试的更多细节,请访问JEDEC的网站http://www.jedec.org/或http://www.memforum.org/index.asp,可以找到详细的DDR规范、白皮书,和其他辅助材料,也可以登录www.tektronix.com/memory,查找关于DDR测试的更多信息。

编辑:吕勇

- 智能手机简介(06-06)

- 关于智能型手机电源管理系统的设计与应用(09-28)

- 高通发布45纳米Snapdragon芯片组(05-07)

- 独立AP架构为智能手机设计增加自由度(05-07)

- 瑞芯推出三款多媒体智能手机芯片解决方案(05-22)

- 智能手机全键盘控制器及其编程(08-08)