一种输出格式可控的多码率LDPC编码器实现

时间:11-06

来源:现代电子技术

点击:

(4)并/串转换模块。SRAA电路的输出为并行数据,对并行数据做并串转换,以便码流控制模块对输出码流的格式进行控制。

(5)同步FIFO。DTMB标准的LDPC码为系统码,输出时,息位在后校验位在前,故需要对信息输入序列进行缓存。当校验位输出完毕后,再从同步FIFO中读敢信息位补在校验位后面,构成完整码字。

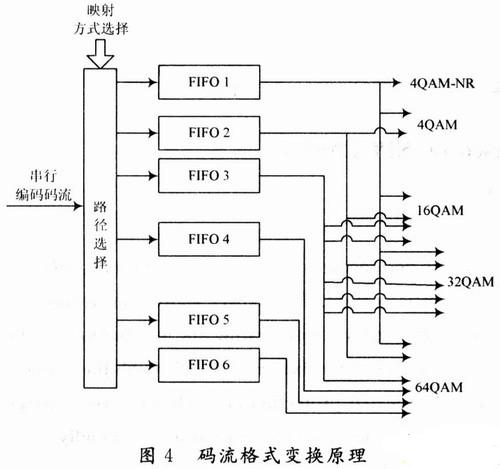

(6)码流输出模块。为了实现与符号映射方式的最佳匹配,编码器输出码流格式必须支持1,2,4,5,6五64QAM四种符号映射方式时,编码器输出的最佳宽度分别为2,4,5,6。考虑到充分利用FPGA中的大量BlockRAM资源优势,在此采用基于乒乓操作的思路,利用6个宽度为1的FIFO来实现串行数据流到指定宽度数据流的转换,结构原理如图4所示。

以编码后进行4QAM映射方式为例,串行的数据流在控制模块输出信号fifo_vaIid的控制下,第1个数据存人1号FIFO,第2个数据存入2号FIFO,然后第3个数据又存入1FIFO,第4个数据存入2号FIFO,如此循环直到FIFO填满,控制模块收到从FIFO返回的full信号时,输出信号data_rd_en打开1号和2号两个FIFO是2位而输入为串行,输出的速度比输入快,当FIFO的数据被读空时,产生一个empty信号给控制模块通知停止读FIFO,此后编码器输出0序列,同时输出数据有效信号code_out_en为0。类似地,对应16QAM,32QAM,4QAM,64QAM可以得到宽度为4,5,6的输出码流。如果使用的是4QAM-NR符号映射.由于编码后要先进行交织,码流串行输出是最佳选择,因此串行的数据无需进行FIFO组的缓存。直接输出即可。

(7)码流输出格式控制模块。根据输入引脚mod-ulation_type选择的符号映射方式,来实现对码流输出模块的乒乓操作。产生控制信号fifo_valid、data_rd_en,同时接收码流输出模块返回的full和empty信号,达到控制编码器输出码流宽度的目的。

3 设计结果与验证

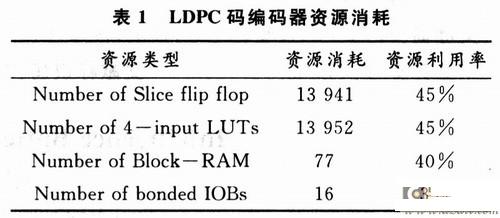

这里的LDPC编码器是在Xilinx公司的XC4VSX35 FPGA芯片下实现的,设计中使用流水线、乒乓操作等技巧提高系统工作的频率,综合后的硬件资源消耗如表1所示。在布局布线中,对相应的管脚和周期进行适当的约束,通过使用不同频率的激励作为输入进行测试,硬件电路核心部分的最高工作频率可达到83 MHz左右,完全符合DTMB标准中的最高时钟频率要求7.56×6=45.36MHz。

验证时,以0.4码率的LDPC码、输出码流格式为6位并行为例,得到时序仿真结果如图5所示。在Testbench中对一次时序仿真的输出码流序列进行保存,并和Matlab中编码的结果比较,LDPC编码器的输出与Matlab计算所得的结果是完全一致的。同理,可以验证其他两种码率在不同的输出格式下,LDPC编码器的编码结果也是正确的。

4 结 语

这里实现了一种码流输出格式可控的多码率LDPC编码器,并验证了编码器的正确性。该编码器不仅同时支持DTMB标准中三种码率的LDPC码,而且输出的码流格式具备1,2,4,5,6位宽度可选,从而实现与4QAM,16QAM,32QAM,64QAM,4QAM-NR五种符号映射方式的最佳匹配,具有较好的通用性,完全可以应用在DTMB系统的发射机中。 (编辑:吕勇)

- 如何通过开源API进行DSP视频处理(02-15)

- 基于DM365的视频编码器的硬件设计(10-15)

- 音视频SoC测试要求与应用介绍(07-20)

- JPEG2000编码器IP核设计,包括具体算法与结构(01-05)

- H.264在ADSP-BF561上的实现与优化(05-27)

- 一种简单串行鼠标控制的单片机实现(03-19)