什么是PCI Express 标准(中)

PCI Express 构架

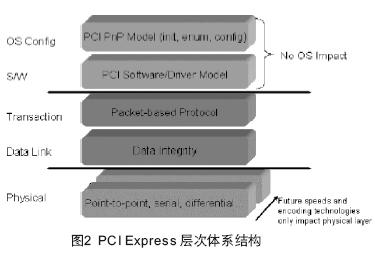

如图 2 所示,即 PCI Express |0">PCI Express 的层次体系结构。它保持了与 PCI 寻址模式(加载-存储体系结构且具有单层地址空间)的兼容性,从而保证了所有现有的应用程序和驱动操作无需改变。PCI Express 配置使用的是PCI 即插即用标准中所定义的标准机制。软件层发出读和写请求,并使用基于数据包、分段传输的协议通过处理层传输至I/O 设备。

链路层向这些数据包添加序列号和循环冗余校验(CRC )从而创建了一个高度可靠的数据传输机制。基本的物理层包括两个单工通道,即传输对和接收对。这个传输对和接收对一起被称为一个信道。2.5 Gb/s 的初始速度提供了在每个PCI Express 信道上每个方向上大约250 MB/s 标准带宽。一旦考虑协议头,这其中大约200 MB/s 由设备用来传输数据。这一速率是大多数典型 PCI 设备的 2 番到 4 番。而且不同于 PCI 的是,只要总线带宽在设备之间共享,每一个设备都 具有此带宽。

物理层

物理层

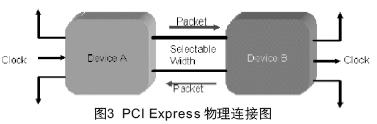

基本的PCI Express 链路包括两个低电压的AC 耦合差分信号对(一个传输对和一个接收对),如图3所示。物理链路层信号使用一个去加重(de-emphasis )策略来减少符号间干扰,从而提高了数据完整性。数据时钟通过使用 8b/10b 的解码策略来嵌入,从而到达极高的数据传输率。初始的信号发生频率是每个方向 2.5 Gb/s (生成1个信号) 而且它将会随着硅工艺的提高而增加至每个方向10 Gb/s(信号在铜线中传输可能实现的最大速率)。两个链路层的 PCI Express 代理在物理层上传输数据包。

图3 PCI Express 物理连接图一个PCI Express 链路层的带宽可能通过增加信号对形成多个信道而线性增长。物理层提供 x1, x2, x4, x8, x12, x16 和x32 信道宽度,理论上它将输入的数据包在这些信道上分配。使用 8b/10b 编码方式,每一个字节在这些信道上传输。数据的分拆和整合对于其他层来说是透明的。在初始化阶段,每个PCI Express 链路通过链路两端代理的信道宽度的匹配和频率操作来建立。在这其中没有固件和操作系统软件的参与。PCI Express 体系结构提供了将来通过速度升级和高级编码技术所带来的性能提升。将来的速度、编码技术或者媒介仅仅会影响物理层。

图3 PCI Express 物理连接图一个PCI Express 链路层的带宽可能通过增加信号对形成多个信道而线性增长。物理层提供 x1, x2, x4, x8, x12, x16 和x32 信道宽度,理论上它将输入的数据包在这些信道上分配。使用 8b/10b 编码方式,每一个字节在这些信道上传输。数据的分拆和整合对于其他层来说是透明的。在初始化阶段,每个PCI Express 链路通过链路两端代理的信道宽度的匹配和频率操作来建立。在这其中没有固件和操作系统软件的参与。PCI Express 体系结构提供了将来通过速度升级和高级编码技术所带来的性能提升。将来的速度、编码技术或者媒介仅仅会影响物理层。

在PCI Express 中使用不同的信道宽度需要用户注意扩展板要求的带宽以及与母板提供的带宽相匹配。除了图形卡以外(通常是X16 ),许多早期的PCI Express 扩展板使用的 X1 的宽度。随着更高的带宽要求,越来越多的板卡将使用更宽的带宽。早期的PCI Express 计算机提供一个X16 的连接器以及一些X1 、X4 、X8 插槽的组合,这由计算机面向的客户所决定。PCI Express 允许在不匹配的信道宽度上进行一些交互操作,这取决于不匹配的方向。在一个较小宽度的连接器上使用更大宽度的扩展板卡是向下插入。例如,利用PCI ,您可以在一个32 位的插槽上插入一个64 位的PCI 板卡。

然而,在 PCI Express 中,向下插入在物理上被扩展板卡和连接器所阻止。另一中不匹配在一个较大的连接器上使用一个较小的扩展板卡是向上插入。向上插入是允许的,但是会受到限制在这种配置下,母板厂商需要支持仅在X1 数据率上的扩展板卡,从而浪费了在具有更快接口速率的扩展板卡上的投资。无论一个特定的母板在向上插入配置时能否在全速率时处理一个扩展板卡,都必须在每种情况下向母板生产商确认。例如,一些母板可以在一个X4 的扩展板卡插入一个X8 或X1 的插槽时,以全速率(X4 )进行处理,然而来自同一厂商的其他母板可能仅以X1 的速率运行。在一个母板既带有集成图形控制器(板载)又带有一个 X16 的 PCI Express 插槽以用于将来图形扩展的情况下,通常不可能在板载图形卡使能的同时使用那个 X16 的插槽。

数据链路层

链路层的主要作用就是保证数据包在 PCI Express 链路上的可靠传输。链路层负责数据完整性并向处理层的数据包添加序列号和循环冗余校验,如图4所示。大部分数据包在处理层初始化。一个基于优先数的、流量控制的协议保证了数据包仅在另一端具有接收这个数据包的缓冲区情况下才能传输,这样就去除了任何数据包的请求以及由于资源限制而引起的总线带宽浪费。链路层会自动的重新收发一个被标记为损坏的数据包。

处理层

处理层

处理层接收软件层的读和写请求,并创建请求数据包发送至链路层。所有的请求都被分段的处理而且一些请求包需要一个响应包。处理层也从链路层接收响应数据包并且将它与原先的软件请求相匹配。每一个数据包都具有一个唯一的标识,使得响应包能够指向正确的源。数据包的格式提供了32 位的存储地址和扩展的64 位地址。数据包也具有诸如"无侦听"、"灵活排序""优先级"等属性,这可能用于将这些数据包在I/O 子系统中以最优的路径传输。

处理层提供4 个地址空间3 个PCI 地址空间(内存、I/O 和配置)和消息空间。PCI 2.2 引入了另一种广播系统中断的方式称为消息信号中断(MSI )。作为PCI 2.2 系统中一种可选的性能, 这里使用了一种特殊格式的内存写处理替代硬连接的边带信号。PCI Express 技术指标重新使用了MSI 概念以作为一种主要的中断处理方式,并且使用了消息空间来接收所有的优先的边带信号来作为带内信号,例如中断、电源管理请求,和复位。其它PCI 2.2 技术指标中的"特殊周期",例如中断确认,也被处理成带内消息。您可以将 PCI Express 消息视为"虚拟的线",因为他们的作用是消除当前平台上所使用的各种边带信号。

- 基于ADSP-TS201S的图像采集处理系统(08-12)

- 高速视频信号的光纤传输系统设计(08-18)

- 基于PCI总线的雷达视频采集方案(10-06)

- 多声道,高音质兼顾的M-AUDIO声卡评测(10-30)

- 破除“万能总线”的神话(01-24)

- 什么是PCI Express 高速串行互联接口标准?(07-02)