高速视频信号的光纤传输系统设计

西安西北核技术研究所(710024) 阮林波 李斌康 郭明安 郝文析

摘 要:针对1000帧/秒高速摄影传输系统需实现数据输出速率600MBps的长距离传输难题,提出了采用CIMT编码方式的光纤数字化传输设计方案。整个系统主要包括数字信号的多路复用、解复用以及PCI数据传输卡三部分。详细阐述了系统的原理及硬软件实现方法,设计实现了两路高速视频数字化信号的15公里远距离传输和计算机实时显示。

关键词:光纤传输 复用 解复用 PCI

高帧频的视频信号不同于普通视频信号,如果采用模拟信号方式传输,它的模拟带宽达到了几十兆甚至一两百兆,这样很难实现远距离传输。而光纤传输容量大、质量高和不易受干扰等特点,在高速数字传输系统中得到了广泛应用。目前国内外针对普通视频信号的光纤传输系统已相当多[1,5],而对非标准的高帧频视频信号光纤传输系统少有报道,特别是两路或多路高帧频视频的单根光纤传输实现则未见报道。

在本文中需要实现两路256×256像素每秒1000帧高速视频信号远距离传输。对于高帧频摄像机,由于它帧频很高,通常采用多路并行的信号输出方式降低数据率,最后通过复用合成为视频信号[2]。为实现远距离传输,文中提出采用数字光纤的复用、解复用和计算机PCI技术实现两路高帧频视频设备产生的15MBps×40路数字信号的传输与视频信号的合成及计算机实时显示。

1 系统原理和结构

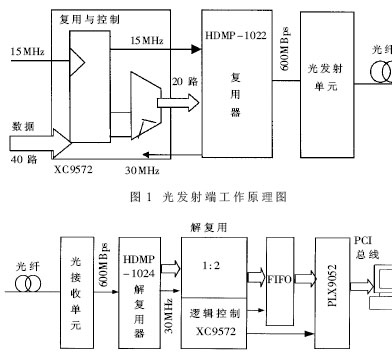

高速视频信号的光纤传输系统主要包括复用、光发射、光接收、解复用、控制电路和PCI传输接口等部分。图1为系统光发射部分工作原理图。

从高速视频采集获得的40路15MBps的数据首先经过XC9572内的2:1复用,形成20路30MBps的二级复用数据提供给HDMP-1022,由其完成信道编码,转换成600MBps的PECL串行数据,驱动光发射模块,完成数据的光纤发射。图2为光接收部分原理图。

解复用芯片HDMP-1024从光纤接收模块接收到的600MBpsPECL数据中提取出20路的并行数据和30MHz的时钟信号,再由XC9572完成二级解复用,同时也为FIFO及PLX9052组成的PCI传输卡提供时序信号,计算机通过PCI总线获得实时高速视频采集数据,并予以显示和处理。

2 硬件设计

系统的硬件设计主要包括光纤传输单元、PCI传输单元和控制单元三部分。

2.1 数字光纤传输单元设计

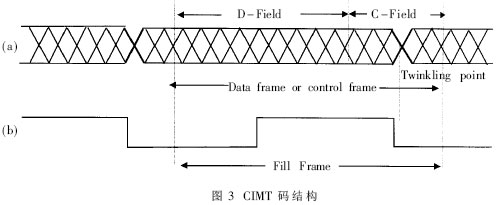

数字光纤传输单元主要完成串并行数据的复用与解复用功能。设计中采取数据通信中的CIMT(Conditional-Invert Master Transition)信道编码方式对数据进行编码。图3显示CIMT码的格式。

CIMT码有三种帧形式:数据帧、控制帧和填充帧。数据帧和控制帧的格式如图3(a)所示,可以发送任意需要传送的数据和控制信息,每一帧都以C-Field(Coding Field)开始,其后接着D-Field(Data Field)。其中D-Field组成的数据位可以是十六位或二十位,本系统采用二十位数据;控制位(C-Field)由四位数据码组成,接收端可以此提取并锁定数据的类型与状态。填充帧是在发射端没有数据信号时以及发射端和接收端建立连接时产生。在三种帧的主瞬变点处是接收端恢复时钟信号的参考点。本系统中选用Aglient公司的HDMP-1022和HDMP-1024作为CIMT码的复用与解复用主要芯片,HFCT-5208作为光发射和光接收器来实现点对点的光纤传输设计。

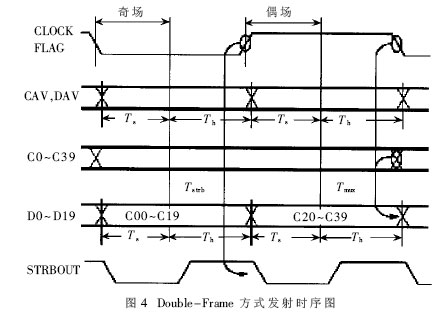

在光发射端设计中采用HDMP-1022的Double-Frame模式实现40路数据的传输,通过二级复用扩展其并行数据的容量为40路。数据在同一时钟控制下同时被复用成一路的高速信号,同时生成另一路按位取反的信号,最后通过其CIMT编码器输出推动光发射器。图4为以Double-Frame方式复用发射的时序图。其中CLOCK(15MHz)是单路数据采集时钟,FLAG表示奇偶场,CAV和DAV表示数据帧和控制帧的控制位,C0~C39表示输入的40路信号,D0~D19是CIMT码的D-Field数据,STRBOUT(30MHz)为芯片锁相后的倍频时钟。

在光接收端部分光接收器将获得的光信号转变为高速电信号并发送给HDMP-1024,由它解复用后提取参考时钟信号STRBOUT(30MHz)、数据信号C0~C39,以及其他的状态控制信号和数据时钟RCLK(15MHz)。图5为Double-Frame光接收端时序图。

2.2 PCI传输单元设计

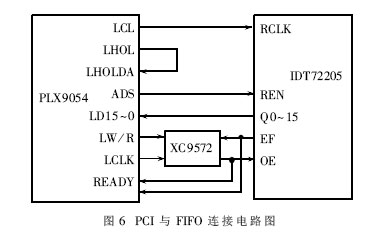

为实现高速视频信号的实时记录,设计中利用了PCI总线技术,PCI控制芯片采用PLX9052,它与FIFO相结合可以实现最高数据传输速率120MBps数字量输入。

PLX9052符合PCI2.1规范,支持低成本从属适配器。内部包括一个64字节的写FIFO和一个32字节的读FIFO,通过读写FIFOs,可实现高性能的突发式数据传输;其局部总线与PCI总线的时钟相互独立,局部总线的时钟频率范围为0~40MHz,PCI的时钟频率范围为0~33MHz;可以通过串行EEPROM提供PCI总线和局部总线的部分重要配置信息。PLX9052支持突发式内存映射传输和单周期的内存或I/O映射传输,利用32字节的直接从设备读FIFO和64字节的直接从设备写FIFO,映射在PCI内存和I/O空间中的地址由PCI基址寄存器设置。而且,局部映射寄存/b器允许将PCI地址空间转换为局部地址空间。图6是PLX9052与FIFO相互连接的电路图,FIFO采用IDT公司的IDT72205。

- 基于ADSP-TS201S的图像采集处理系统(08-12)

- 基于PCI总线的雷达视频采集方案(10-06)

- 多声道,高音质兼顾的M-AUDIO声卡评测(10-30)

- 破除“万能总线”的神话(01-24)

- 什么是PCI Express 高速串行互联接口标准?(07-02)

- 什么是PCI Express 标准(上)(06-30)