基于USB 2.0集成芯片的H.264解码器芯片设计

3 电路设计原理图

图4为本设计的电路设计原理图,原件按左起以及上起顺序分别为:CY7C68013A芯片、电源耦合电容组、USB 2.0标准接口、标准RS232串行口、外部晶体振荡器和HIN232串口芯片。本设计是按照这一电路原理图制作电路板图,完成USB 2.0的功能的。

图4 电路设计原理图

FPGA上解码器与USB接口模块的设计

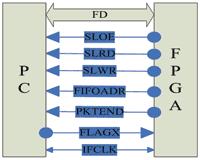

SLAVE FIFO的模式下,FPGA可以主动决定是否有必要读取USB内部FIFO中的数据,而不仅仅是被动的接受PC发送的数据。如图5所示,控制方式:SLOE、SLRD和SLWR作为EP的读写信号与使能控制信号。FIFOADR[1:0]作为4个EP的选择信号,即选择当前操作的目标EP。PKTEND是FPGA主动命令USB芯片向上位PC发送数据的控制端。FLAGX(X=A,B,C,D)表示当前选中的FIFO的空满信息。FD(8位或者16位)为双向的数据传输口。FPGA接口控制这些端口,达到对USB进行操作的目的。

图5 解码器与USB接口

FPGA接口中,本设计还定义了一个深度为256,宽度为32位的FIFO(内部FIFO)。原因在于:本设计中SRAM和DRAM部分要不断地被解码器调用,这样就导致存储单元被占用。此时USB是无法对存储单元操作的。所以在FPGA接口中,先将多个USB传输的数据FD(8位或者16位)拼接成32位数据存入内部FIFO,当SRAM和DRAM空闲时,再向其传输。这样的处理,使得USB传输不依赖于存储单元的工作状态,进一步提高了USB传输的速度,以满足传输的要求。

设计验证及结果分析

当开发完Windows操作系统下的USB驱动程序后,本设计成功的利用EZ-USB芯片与Virtex II FPGA完成了视频数据的传输工作。并且在FPGA工作的66MHz以下的频率时,完成了对H.264格式视频的实时传输、解码。传输速率的检测中,USB对大批量数据的传输可以达到33MB/s以上的速度,完全适应解码器的要求。

设计分析:本设计利用了两级的FIFO,充分的发挥了USB 2.0的速度优势。设计方案解除了传输与解码过程中的瓶颈,实现了无缝连接。不足之处是由于USB芯片的Slave FIFO模式限制,PC与解码器直接必须使用命令交互的方式进行通信,占用了一定的带宽。在命令过于频繁的状态下,效率不高,但对大批量数据传输影响很小。

结束语

验证平台下成功,并且实际通过多种压缩率的源码文件测试,实现了平均33MB/s,最高40MB/s的速率。完成并且超过了设计要求。

H 264 USB MPEG4 FPGA 1080i 相关文章:

- DVI与HDMI:视频传输的数字化革命(08-15)

- 大规模IPTV点播系统解决方案(08-18)

- 数字音视频编解码技术标准AVS(08-19)

- 嵌入式设备的静止图像编码(08-18)

- 基于Blackfin533的H.264编码(08-18)

- 全球手机电视三大技术标准对比分析(08-19)