非压缩数字视频传输系统的设计

速串行数据进入Rx后,片内的时钟--数据恢复电路(CDR)从输入数据提取时钟,恢复出数据。CDR电路锁住REFCLK的频率,与抽样后的输入信号相位对齐。恢复后的数据进入解复接电路,时钟发生器根据码流速率产生内部电路所需的所有时钟。此时串行数据解复接为并行数据,再进入译码器译码,然后输出并行码。

信号经一次复接后,2路视频和4路音频复接为13路并行的数字信号,同时,为了准确恢复音频信号,保证接收端和发射端信号与复接时钟之间的相对关系不变,我们将复接时用到的时钟F1和F2也作为数据与信号并行传输,在接收端得到RF1和RF2。这样,加上2路时钟信号,总共15路数字信号进入二次复接芯片HDMP1032A的数据位。由HDMP1032A出来的1路串行数据经光纤传输进入HDMP1034A,通过其内部处理,在接收端得到的仍然是15路数字信号,即进入HDMP1032A的并行信号。这样,音视频信号的二次复接和一次解复接已经由HDMP1032/4A芯片组完成。

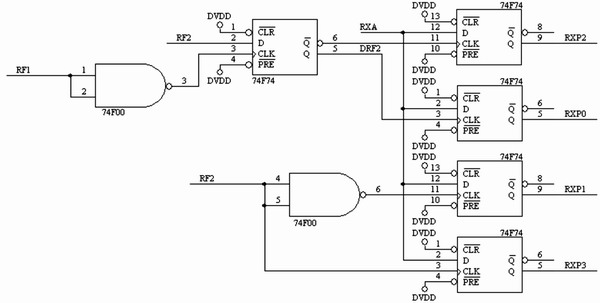

图3 音频二次解复接的电路原理图

音频二次解复接的实现

HDMP1034可自动产生两个互为反相的RXCLK0和RXCLK1,作为所有输出信号的标志信号,所有的恢复信号的相位均以这两个信号作为参考。这对于得到用于恢复各路音频的时钟信号非常重要。图2所示的是输出信号与RXCLK0和RXCLK1之间的时序关系。RX[0-15]表示HDMP1032/4A芯片组中可作为信号传输的16位并行数据位,它们与RXCLK0的下降沿存在td、典型值为2ns的延迟。事实上,作为芯片时钟输入的TXFLAG经过芯片组后得到的RXFLAG同样与各数据位相位一致。

从串行信号恢复出的各信号必须遵循的原则是用复接时用到的频率去恢复出串行流中包含的各信号。因此,首先用同样是Tx恢复出的16.384MHz的RX16MA将数据信号和外部扩展信号EX分离开,得到RXA。为了能准确地恢复RXA,所选用的16.384MHz时钟的边沿应该尽量靠近RXP[0-3]数据包的中间部分。处理的办法是将RXFLAG做为数据位,RXCLK1做为时钟,经过一个D触发器,得到16.384MHz的RX16MA,这样,RX16MA与RXAE之间存在约为5ns的延时。

对于RXP[0-3]的恢复选用的是两个4.096MHz的时钟,具体的电路如图3所示。最后用于RXP[0-3]解复接的4个时钟信号分别是DRF2及其反相信号,RF2及其经过与非门之后的信号。其中,DRF2及其反相信号分别解出RXP0和RXP2,RF2及其经过与非门之后的信号分别解出RXP3和RXP1。因为4路音频复接成的串行信号速率为16.384Mbps,因此,对相邻两路音频信号解复接的两路时钟信号应存在一个周期的延迟,对应到解复接采用的4.096MHz的时钟,即为1/4个周期的延迟。

这样,首先将4路音频与1路扩展信号分离,然后进行RXP[0-3]的解复接,最后恢复出了4路音频信号。

结语

本方案具有简单、实用、可靠性高、成本低等特点,已经成功运用于传输多路音视频及数据信息的光端机设计中。视频传输质量达到广播电视水平;音频传输质量足以满足专业级的立体声传输要求(失真<-75dB、S/N>75dB、20Hz~20kHz带内平坦度<±0.5dB)。

参考文献

1. Agilent HDMP-1032A/1034A Transmit/Receive chip data sheet of [Z]

2. 李泉,文鹰.利用FPGA与串行/解串行芯片HDMP1032/1034设计数字视频的复/分接[J].电子技术,2003,(2): 43-46

- 浅谈双绞线视频传输的应用基础以及特点(03-07)

- IPTV视频传输质量集中监测系统的研究(04-30)

- 基于同轴视频传输技术原理与实际应用(07-02)

- 关于视频传输的技术问题解决方案及应用案例设计汇总(07-14)