逻辑分析仪基础

显示"有效时钟或控制信号"期间的信号活动是"什么"。

状态分析仪侧重于查看指定执行时间内的信号活动,而不是与时序无关的信号活动。

这就是为什么状态分析仪需要对与被测设备时钟信号"同步化"或同步的数据进行采样。

对于微处理器,数据和地址可以出现在相同的信号线上。要采集正确的数据,逻辑分析仪必须对数据采样加以限制,使之只在所需的数据有效并出现在信号线上时进行。为此,它会从相同的信号线上采集数据样本,但使用来自被测设备的不同采样时钟。

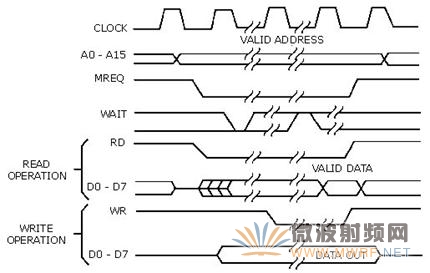

示例:以下时序图表明,要采集地址,分析仪需要在 MREQ 线下降时进行采样。

要采集数据,分析仪需要在 WR 线下降(写周期)或 RD 线下降(读周期)时进行采样。

图7 状态采集

触发状态分析仪:

与定时分析仪相似,状态分析仪也具有限定要存储的数据的功能。如果我们正在查找地址总线的上限和下限的特定码型,当分析仪找到该码型时,我们可以通知分析仪开始存储,并且只要分析仪的内存未满就一直存储。

简单触发示例:

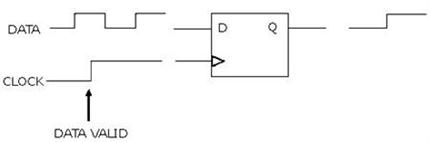

请看下面显示的"D"触发器,在正值的时钟沿出现之前,"D"输入上的数据是无效的。因此,时钟输入为上限时,触发器的状态才有效。

图8 D触发器

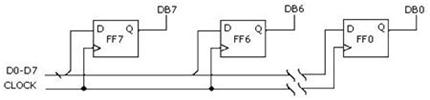

现在,假设我们有并行的八个此类触发器。如下所示,这八个触发器都连接到同一时钟信号。

图9 接收器

当时钟线上出现高电平时,所有这八个触发器都会在其"D"输入处采集数据。此外,每次时钟线上出现正电平时都会发生有效状态。下面的简单触发指示分析仪在时钟线上出现高电平时在 D0 - D7 这几条上收集数据。

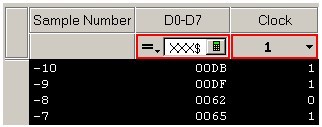

图10 总线收集的数据

高级触发示例:

假设想查看地址值为 406F6 时内存中存储了哪些数据。对高级触发进行配置,以在地址总线上查找码型 406F6(十六进制)以及在 RD(内存读取)时钟线上查找高电平。

图11 高级触发设置

在配置 Edge And Pattern trigger(时钟沿和码型触发)对话框时,尝试将该操作看作是构造从左向右读取的句子。

Find the first occurrence of a Bus named ADDR, and on All bits a pattern that Equals 406F6 Hex, And a Signal named RD with a High level.Then Trigger and fill memory with Anything.

Pod、通道和时间标签存储

Pod和通道的命名约定:

Pod是一组逻辑分析仪通道的组合,共有17个通道,其中数据16个通道,时钟1个通道。逻辑分析仪的通道数是Pod数的倍数关系。34通道的逻辑分析仪对应两个Pod,68通道逻辑分析仪对应4个Pod,136通道逻辑分析仪对应8个Pod。

对于模块化的逻辑分析仪(或称为逻辑分析系统),以 16900 系列逻辑分析系统为例,对应关系如下:

1.插槽从上到下以 A 至 F 字母命名。

2.有一条标有 Pod 2 的电缆连接着每一个逻辑分析仪模块。知道某个Pod连接到哪个插槽很重要,因为如果在插槽 A 和 B 中都有逻辑分析仪模块,则将有两条盒电缆标有 Pod 2,但操作界面应用程序会把一条记作 Slot A Pod 2,把另一条记作 Slot B Pod 2。分清这两条电缆很重要。

3.Slot A Pod 2 等于 Pod A2。A2 与 Slot A Pod 2 可互相替代;同样,D1 与 Slot D Pod 1 也可互相替代。

4.时钟Pod (Clock Pod) 由模块中所有Pod的所有时钟通道组成。

5.每个Pod各有一个时钟通道。所有时钟通道按 Clk1、Clk2、Clk3 等进行编号。如果某逻辑分析仪模块有两个逻辑分析仪卡,每卡有四个Pod,则该逻辑分析仪的时钟通道标记为 Clk1 至 Clk8。

6.除了 Clk1 外,时钟通道还可标记为 C1。C1 和 Clk1 是一样的。

在 16900 系列逻辑分析系统中,请勿混淆时钟通道 C2 与 Slot C 中的 Pod 2,后者记作 Pod C2。对于时钟通道,C 是 Clock 的缩写,不是 Slot C 的缩写。

为什么有时Pod会丢失?

导致所有Pod对逻辑分析仪模块均不可用的原因有多种:

在状态采样模式中,在选择了一般状态模式采样选项的情况下,选择最大采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为最大值的一半(或更小)将返回Pod。

在状态采样模式中,在选择了高速状态模式采样选项的情况下,会将一个Pod对保留用于时间标签存储。

在定时采样模式中,在选择了跳变/存储限定定时模式采样选项的情况下:

选择了最小采样周期时,会将一个Pod对保留用于时间标签存储。

选择了除最小采样周期之外的采样周期时,选择最大采集内存深度需要将一个Pod对保留用于时间标签存储。在这种情况下,将内存深度设置为最大值的一半(或更小)将返回Pod。

该模块是已分离的逻辑分析仪的一部分。在这种情况下,Pod位于分离分析仪的另一半模块中。

状态模式