“后CMOS”时代成摩尔定律终结者?

在英特尔(Intel)负责晶圆厂业务的最高长官表示,摩尔定律(Moore’s Law)有很长的寿命,但如果采用纯粹的CMOS制程技术就可能不是如此。

"如果我们能专注于降低每电晶体成本,摩尔定律的经济学是合理的;"英特尔技术与制造事业群(technology and manufacturing group)总经理William Holt,在近日于美国旧金山举行的年度固态电路会议(ISSCC)上对近3,000名与会者表示:"而超越CMOS,我们将看到所有东西的改变,甚至可能是电脑的架构。"

Holt婉拒分享他所说的"丰富多样化"后CMOS (post-CMOS)技术,会有哪些获得晶片制造商采用、或是何时采用;那些新技术包括自旋穿隧场效电晶体(SPAN tunneling FET)、铁电FET、自旋电子、新一代三五族材料…等等。但他声明这些新技术不会出现在英特尔正在制作处理器圆形的10nm制程。

在一般情况下,工程师们会尽可能延展CMOS技术的寿命;Holt表示,长期来看,晶片制造会是不同技术与传统CMOS的混合:"我们将看到混合的操作模式…(晶圆的)某些部份采用CMOS技术,相同晶圆上的新元件则为不同的优势最佳化。"

他对于将照亮接下来十年半导体产业发展路径、显然还需要庞大研究工作的技术提供正面看法:"我不能告诉你在那些(后CMOS)技术中,哪个排第一或是最棒,但是我们看到其中丰富的可能性…将在接下来几年提供大量的机会,让我们在打造零件所需的技术上取得重大进展;而挑战在于厘清如何实现它们。"

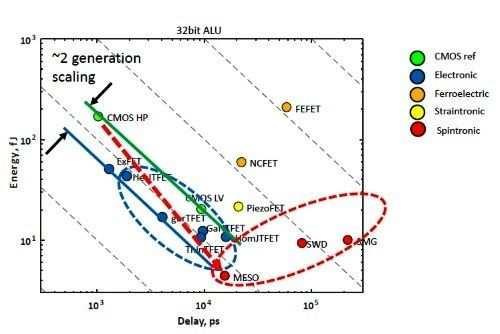

到目前为止还有个大挑战,是所有的后CMOS替代技术都有助于降低功耗,这是一个首要考量,但它们的执行速度显然比起CMOS电路缓慢得多;Holt拿这个问题与一个世代以前工程师为了因应当时紧迫的功率需求、从双极架构转为新的复杂CMOS的状况比较。

很多种类的后CMOS技术都能降低功耗,但也导致延迟

Holt表示,产业界需要专注于降低功耗与降低每个电晶体的成本;他重申英特尔已将22nm与14nm制程节点电晶体成本降低30%、稍优于业界水准的声明,不过开发最近几个新制程节点的成本增加幅度,由传统的10%增加到了30%。

他指出:"现在预测7nm节点的细节还太早,但我们可以说,我们在7nm节点的每电晶体成本降低幅度,在历史线的范围内可能会更多──我们看到了一些降低成本的可行途径。"

在专题演说之后,Holt澄清,对英特尔7nm节点的预测,目前落到延续自传统电晶体成本下降趋势、到英特尔在22nm与14nm节点收获的些微改善之间的范围内:"不确定因素还很多,所以我们不知道我们会落在哪个点上。"

英特尔一直都没有放弃希望,认为可能在7nm制程量产开始后的某个时间点开始采用超紫外光(EUV)微影技术;EUV可能对7奈米制程的成本带来显着的影响,降低对多重图形(multi-patterning)的需求。

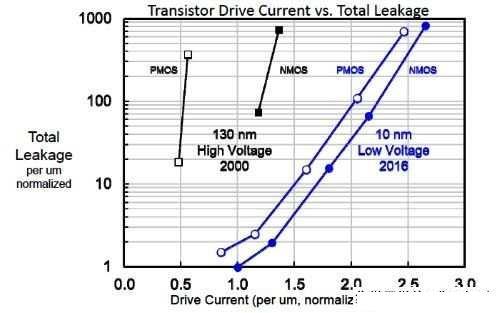

此外Holt还指出英特尔10nm制程将支援5个等级的电压阈值,在既定节点内的最佳化点(optimization points)之多样化,可能会随着后CMOS技术的加入而提升。

Holt表示,英特尔的10nm制程将支援五种电压阈值,提供更多功率选项迟

- 摩尔定律将死带来全球产业链重新洗牌机会(03-08)

- 晶体管进入3-D时代!(05-06)

- 美物理学家称摩尔定律将在10年内崩溃(05-04)

- 晶圆技术将摩尔定律延伸至20纳米(06-18)

- 奈米碳管:半导体持续摩尔定律步伐前进动力?(11-05)

- 摩尔定律快不行?MIT:莱特定律更准(03-12)