Imagination也是蛮拼的,P5600要打造CPU新标杆

两个月前,我参加了首次在日本举行的Imagination高峰论坛,并在活动结束后准备回家。在我等待登机返回英国时,看到了日产汽车的一个广告牌-"如果全世界跑得最快的男人还能更快,会怎样?"我心里想着,这真是个有趣的问题。

几个星期之后,工程团队的同事寄了一封电子邮件给我,通知我说MIPS P5600已经以破纪录的5.6 CoreMark/MHz per CPU分数成为CoreMark排行榜的第一名。

这款全球速度最快的单线程CPU跑得更快了!

它的性能提升并不是意外。就像日产一样,追求完美一直是我们的目标,即使我们已经是业界最好的了;P5600现已成为CoreMark的新冠军,打破了之前由我们获奖的MIPS proAptiv处理器所创下的最高分数。

这一结果已经获得EEMBC的认证。EEMBC是顶尖的、且历史悠久的嵌入式处理器基准测试组织,负责设计与维护CoreMark基准测试。在他们的网站上你可以找到完整的认证结果清单。

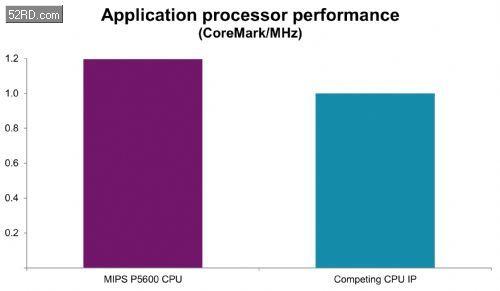

仔细看了这份新结果,我们发现,MIPS P5600 CPU可比其直接竞争的产品提供高20%的性能,而且面积显着地缩小。

MIPS P5600能以更小的面积提供高20%的原始性能

MIPS P5600能以更小的面积提供高20%的原始性能

MIPS P5600的CoreMark/MHz t分数甚至比英特尔的台式机CPU产品还要高。举例来说,Intel? Core? i7-2640M处理器在2.8 GHz,能达到14513.79 CoreMark,也就是5.18 CoreMark/MHz 比MIPS P5600的最新结果低了约10%。

在所有的可授权CPU中,MIPS P5600拥有最高、且经过验证的CoreMark分数。

如此前所未有的性能效率水平,将能为移动、家庭娱乐、网络、汽车以及许多其他采用MIPS-based嵌入式处理器的功耗敏感应用进一步提升性能。

更重要的是,这些优异的结果是利用最新、现有的GCC编译器就能达到的。不管是合作伙伴的原始码还是Imagination的SDK,我们所有的客户都能取得这一高性能工具链。这样的做法与我们的竞争对手完全不同,他们必须采用昂贵、封闭的工具链才能获得最佳的基准测试分数。相反地,Imagination专注于构建能够快速、有效提供性能的开放式生态系统,这对缩短移动与嵌入式应用的上市时间来说,是一个重要的考量。

MIPS P5600简介

P5600是MIPS Warrior P-class 处理器系列产品的成员之一,是专为移动与嵌入式应用提供终极性能所设计的。

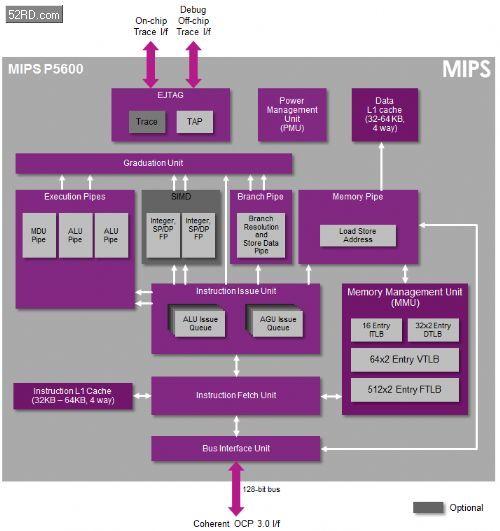

MIPS P5600采用强大、具有丰富特性的微架构设计

P5600是以MIPS架构Release 5为基础的32位CPU,并包含多项独特特性:

快速128位SIMD引擎:可加速多媒体处理与其他的矩阵型运算。

完整的硬件虚拟化技术:可支持多个完全独立、且平行运行的客户端操作系统。

增强的安全性:针对消费类与企业应用,此特性包含可在单一CPU上支持多重TEE(可信运行环境)的能力。

同类最佳的先进分支预测机制、可获得最佳性能的TLB分页表(page table)高速硬件、可为内存密集数据移动惯例增加2倍性能的指令绑定(instruction bonding)。

增强虚拟寻址(EVA):更灵活地使用虚拟地址空间,能轻松、有效地使用内存;延伸实体寻址(XPA)可完全利用最高达1TB的内存容量(40位)。

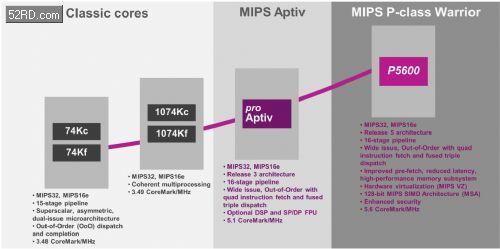

这款高端MIPS CPU同时也是我们第三代多指令执行(multi-issue)、乱序(Out-of-Order,OoO)、可完全合成处理器的系列产品之一。下图所示为长期以来高性能MIPS CPU的演进过程,从74K和proAptiv一直到今天。

高端32位MIPS CPU的演进

MIPS P5600比前一代的proAptiv CPU新增了多项功能提升,包括增强的提取效率、缩短的L2缓存延迟以及预提取功能。此外,还改善了缓存重播与内存歧义消除(disambiguation),能提升各种真实世界的性能(如内存复制性能)。

我们对于新款MIPS Warrior CPU不断创下的破纪录性能感到非常骄傲。这一成果是基于我们长期设计高性能MIPS CPU才能实现的。今后,指令集架构的进展(如Release 6)以及内存子系统与微架构的持续创新,让此产品精益求精,取得更佳的结果。

通过结合MIPS Warrior CPU、PowerVR多媒体IP以及Ensigma 连接性IP,系统工程师将能开发出最先进的嵌入式处理器,并以更低功耗与更小面积实现同类最佳的性能。

- 台积电满脸“苹果光”(05-06)

- 智能手机陷入“千机一面”怪圈(06-08)

- CPU/APU:一场无声的反垄断技术较量(06-21)

- 移动设备纷纷采用多核CPU遭质疑:性能过剩(01-12)

- 系统级芯片SoC真的能取代传统CPU?(04-26)

- 国产CPU:放手一搏正当时(05-11)