28nm器件三大创新,Altera期待超越摩尔定律

时间:01-08

来源:电子工程专辑

点击:

随着TSMC 28nm全节点工艺即将量产,其合作伙伴Altera日前宣布了其产品线将转向28nm节点的策略部署。据了解,TSMC 28nm全节点有两个平台:低功耗(LP)和高性能(HP)。一般而言, LP平台适合基带和应用处理器等低功耗器件,而基于高K金属栅技术的HP平台则适合微处理器和FPGA等。

Altera亚太区高级市场经理罗嘉鸾(Jennifer Lo)透露,Altera高端的Stratix产品未来无疑将采用TSMC的28nm高性能平台进行生产,中端Cyclone会选择28nm低功耗平台,而Mercury产品线的平台归属则尚在探讨过程。由于Altera针对其将采用TSMC 28nm平台生产的器件进行了大量的单一功能的流片测试进行评估,因此相信即将推出的采用了"嵌入式HardCopy模块"、"部分重新配置"以及"嵌入式28-Gbps收发器" 三大创新技术能够极大地扩展28nm FPGA的密度和I/O性能,并进一步巩固相对于ASIC和ASSP的竞争优势。

创新结构超越摩尔定律

尽管一些媒体宣传TSMC 28nm为其第一代全节点工艺,但罗嘉鸾指出TSMC 40nm实质上已经是全节点工艺了。由于TSMC赋予28nm平台全新全节点的定位,Altera也已经着手针对新工艺平台进行FPGA产品内部逻辑架构的重布局。《电子工程专辑》记者从TSMC资料了解到,如果半导体器件生产工艺只是从40nm过渡到28nm,性能加速只是30%左右。

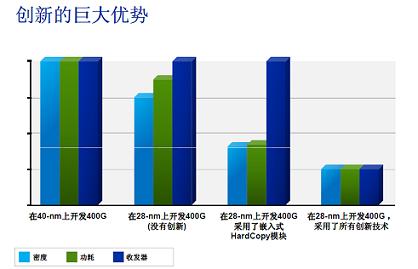

然而,罗嘉鸾指出:"以在FPGA上实现400G收发器为例,Altera结合了这三种创新技术的器件在密度、功耗等方面将可突破摩尔定律限制,解决创新应用的带宽挑战。"

Altera独特的可定制硬核IP模块HardCopy功能可用于实现增强标准或者需要大量逻辑的功能,例如接口协议、专用功能和专业定制IP等。嵌入式HardCopy模块帮助用户缩短了设计面市时间,同时降低了成本和功耗。对于Altera而言,这一创新使其能够面向特定市场迅速开发不同型号的各种产品。

利用部分重新配置功能,设计人员无需关断系统就可实现部分FPGA逻辑的重新配置,不但降低了功耗和成本,而且在FPGA中去掉了那些不同时工作的功能,因此还提高了有效的逻辑密度。Altera在其Quartus II设计软件的渐进式编译设计流程顶层构建了新功能,从而简化了部分重新配置过程的复杂实现。

延续在嵌入式收发器技术上的领先优势,Altera开发了28-Gbps嵌入式收发器,这将应用在即将推出的28-nm FPGA中。这一高速收发器将帮助用户实现单片400G系统等下一代设计,而不需要采用昂贵的外部元件。

扩大定制市场份额

PLD(可编程逻辑器件)市场规模已超过30亿美元。排除PLD供应商无法触及的手机和PC相关的特定消费类的480亿美元ASIC/ASSP市场,Altera估计PLD业者可进军并赢取约280亿美元市场规模中的一些机遇。罗嘉鸾表示, Altera的愿景是在不久的将来依靠结合创新技术的先进工艺产品能够从目前定制器件市场第七位排名晋升到第四位。

发布者:博子

Altera亚太区高级市场经理罗嘉鸾(Jennifer Lo)透露,Altera高端的Stratix产品未来无疑将采用TSMC的28nm高性能平台进行生产,中端Cyclone会选择28nm低功耗平台,而Mercury产品线的平台归属则尚在探讨过程。由于Altera针对其将采用TSMC 28nm平台生产的器件进行了大量的单一功能的流片测试进行评估,因此相信即将推出的采用了"嵌入式HardCopy模块"、"部分重新配置"以及"嵌入式28-Gbps收发器" 三大创新技术能够极大地扩展28nm FPGA的密度和I/O性能,并进一步巩固相对于ASIC和ASSP的竞争优势。

|

| Altera亚太区高级市场经理罗嘉鸾 |

创新结构超越摩尔定律

尽管一些媒体宣传TSMC 28nm为其第一代全节点工艺,但罗嘉鸾指出TSMC 40nm实质上已经是全节点工艺了。由于TSMC赋予28nm平台全新全节点的定位,Altera也已经着手针对新工艺平台进行FPGA产品内部逻辑架构的重布局。《电子工程专辑》记者从TSMC资料了解到,如果半导体器件生产工艺只是从40nm过渡到28nm,性能加速只是30%左右。

然而,罗嘉鸾指出:"以在FPGA上实现400G收发器为例,Altera结合了这三种创新技术的器件在密度、功耗等方面将可突破摩尔定律限制,解决创新应用的带宽挑战。"

|

利用部分重新配置功能,设计人员无需关断系统就可实现部分FPGA逻辑的重新配置,不但降低了功耗和成本,而且在FPGA中去掉了那些不同时工作的功能,因此还提高了有效的逻辑密度。Altera在其Quartus II设计软件的渐进式编译设计流程顶层构建了新功能,从而简化了部分重新配置过程的复杂实现。

延续在嵌入式收发器技术上的领先优势,Altera开发了28-Gbps嵌入式收发器,这将应用在即将推出的28-nm FPGA中。这一高速收发器将帮助用户实现单片400G系统等下一代设计,而不需要采用昂贵的外部元件。

扩大定制市场份额

PLD(可编程逻辑器件)市场规模已超过30亿美元。排除PLD供应商无法触及的手机和PC相关的特定消费类的480亿美元ASIC/ASSP市场,Altera估计PLD业者可进军并赢取约280亿美元市场规模中的一些机遇。罗嘉鸾表示, Altera的愿景是在不久的将来依靠结合创新技术的先进工艺产品能够从目前定制器件市场第七位排名晋升到第四位。

|

- IDT 成为公认的网络搜索引擎全球市场的领导者(06-23)

- Altera 推出首款串行 RapidIO 2.1 IP 解决方案(10-20)

- Altera推出首款符合TüV的工业安全数据套装(02-03)

- Altera Stratix V FPGA提供RLDRAM 3存储器支持(07-04)

- Altera荣获《中国电子报》“最佳3G通信FPGA供应商”奖(05-08)

- Altera荣获TechAmerica基金会“美国技术奖”(05-22)