IC竞争日益激烈,芯片反向设计助你跑赢对手

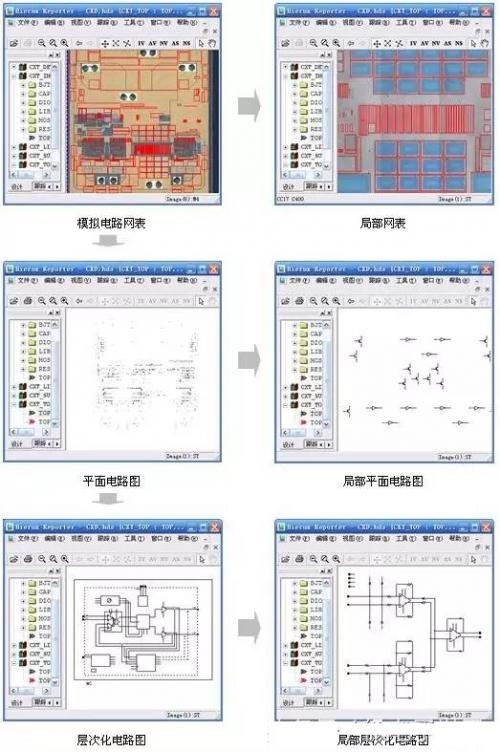

芯片电路整理

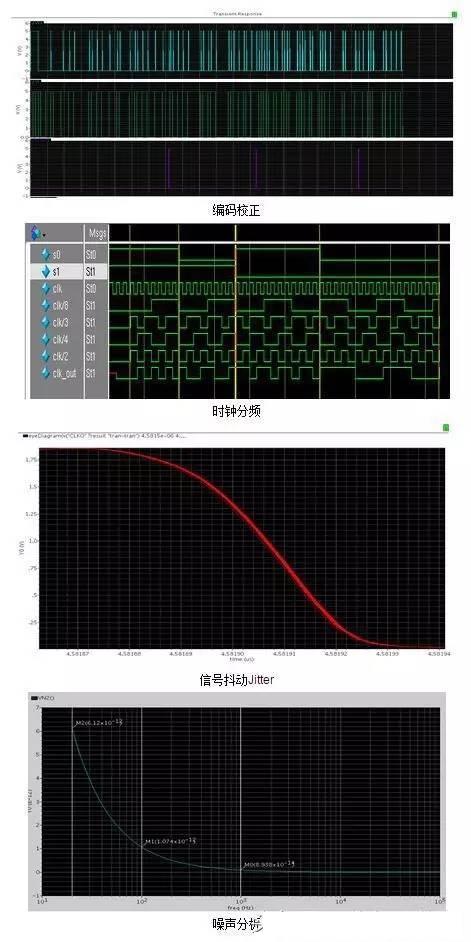

电路仿真及修改

电路整理好了,下一步就是进行电路的仿真及修改了,根据工艺选择步骤选择的工艺来进行。先说明一下这阶段所使用的工具:

1、cadence spectre,一般集成在cadence ic5141里面,是模拟电路仿真工具(ps:最原始的版本是集成在IC5141内部,但功能不全,所以需要单独安装新版本,软件名为MMSIM61,随着版本的升级,它的名字也在修改),当然,数字电路也可以进行仿真,数字电路的本质还是模拟电路;

2、synopsys公司的 Hspice,与spectre一样的仿真工具,另有些差别。

3、Mentor公司的 Modelsim,主要在windows上使用,用于verilog网表的仿真。

模拟电路仿真工作流程:在cadence中搭建好仿真环境,设置好仿真参数,选用spectre或者hspice,然后就可以进行仿真的。另外,也可以将电路导出成CDL网表,拷贝到Windows上,用Windows版本的Hspice进行仿真,这样做的优点是Windows易于操作。另外说明一下spectre和hspice的一项区别。spectre仿真的时候会保存所有电路节点的数据,这样做优点是方便查看各个节点的数据,缺点是仿真消耗的时间太长,保存的数据文件太大,这一点在遇到大型电路的时候会很耗时(不知道最新版本改进这一点没有,鄙人没有用过最新版的spectre)。hspice仿真之前可以自己选定所要查看的节点,这样做就可以减少仿真时间和减小数据文件的大小。

数字电路仿真工作流程:在virtuoso schematic中将整理好的电路路中数字电路部分导出成网表文件,再拷贝到windows系统上进行仿真。windows系统上数字电路网表的仿真采用Modelsim。(这么做的原因是linux系统不太方便)使用Modelsim仿真,最重要的是写好testbench(貌似这句是废话)。

关于电路的修改,这部分其实不好总结,因为每一款芯片都有不同的参数,所要修改的地方都不太一样,我所知道的是,必定要考虑修改的地方往往都是有关模拟电路的,例如,时钟振荡、复位电路、开漏输出管、带隙等,修改的目的是为了与当前所选用的工艺适配,以满足芯片datasheet的参数要求。另外,数字部分的电路其实一般来说是不需要修改的,但有时为了节省版图面积,会缩小寄存器管子的尺寸,毕竟缩小一个,就等于缩小了几十个。这一阶段其实是一个不断的迭代过程,它要和版图绘制结合起来,这样才能够保证芯片功能和性能的完整。

电路仿真

版图绘制

这部分在电路整理完之后就可以开始进行了,并配合电路仿真与修改,逐步晚上版图的绘制。该阶段所使用的主要工具有 1、cadence ic5141的版图绘制软件;2、cadence Dracula Diva或者Calibre,这两个用于版图DRC(设计规则检查)、LVS(版图一致性检查);一般而言,calibre会更加常用一些,毕竟这可是Mentor公司的招牌软件之一。在版图绘制好并进行各种检查无误之后,就可以tapeout,准备流片了。

测试规范

IC设计师在芯片tapeout之后就要准备制定CP测试规范了,这是接下来CP测试流程的总纲,非常重要。测试规范的测试项主要来源于芯片datasheet,将重要的参数设置为测试项,并规定参数的合理分布范围以及每一个测试项的测试方法(流程)。这些测试参数以及测试方法将决定CP测试开发时所用到的测试环境ATE(auto test environment)。

CP测试开发

根据测试规范,可以选定所需要的测试工具以进行整个测试环境的搭建工作。我所知道到用于芯片测试的测试仪有JUNO DTS-1000,ASL1000,V777,STS8200等。每一种测试仪适用于不同种类的芯片测试,测试仪主要分为数字测试,模拟测试,数模混合测试这三大类。

CP测试开发所需要做的工作有:

1,测试仪的选择(ps:这个阶段还要考虑一个重要的因素就是一次测试多少颗裸芯,也就是CP测试常说的多少个site,这关系到后续测试程序的编写,以及DUT板的制作,非常重要);

2,根据测试仪开发测试程序;

3,制作测试裸芯片用DUT板,扎PAD位的针由测试厂制作并焊接在DUT上(ps:DUT板有时候也叫针卡);

4,自制测试仪(可选),当测试仪并不能完成某些特殊测试项的要求时,还得自己制作测试仪。例如,红外接收芯片测试所需要用到的扫频仪,若采用非自制扫频仪,测试时间将非常长,必须自己制作。

5,测试数据的分析。对测试数据的分析有助于对测试方法的改进和对芯片设计的改进。CP测试在整个芯片反向设计中占据着重要位置,所花费的人力、物力是非常多的,还需要频繁和测试厂交流,所以CP测试显得非常复杂。在CP测试开发完之后,会进行COB测试,之后才进行CP测试的调试阶段,以及正式批量测试阶段。

- 基于P89C61x2/ISP1581的USB接口电路的设计(02-13)

- 行波管关断方式对应用系统可靠性的影响(06-24)

- 基于VME总线的RDC接口电路设计(06-29)

- 单芯片集成电路优化自适应转向大灯系统的设计 (07-12)

- 单片机应用系统的抗干扰技术(08-07)

- 基于FPGA的线阵CCD驱动器设计(11-26)