TI:使用CLT工具优化C6000代码

以参照以下实例。

4.实例教程

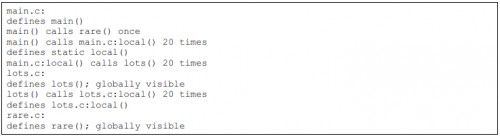

该实例主要由三个C文件组成,

实例中使用DSP计数器TSCL来统计cycle数,子函数放在sub目录下。

使用实例的步骤如下,

1.编译代码

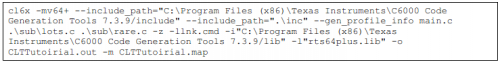

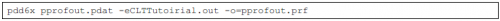

使用TI编译器对该实例进行编译,为了产生用于profile的信息,需要在编译时增加--gen_profile_info选项。如果使用命令还形式,命令行下运行Compile.bat文件,cl6x的具体参数可以参考spru186和spru187两篇文档,一般可以在编译器的安装目录下找到他们,如C:\Program Files(x86)\Texas Instruments\C6000 Code Generation Tools 7.3.9\doc。

同时在目录下生成OBJ和ASM文件,这个和我们的实验关系不大,可以不用关注。out文件是一会需要下载到芯片里运行的可执行文件,而map文件用于帮助我们定位profile信息存放的内存地址。

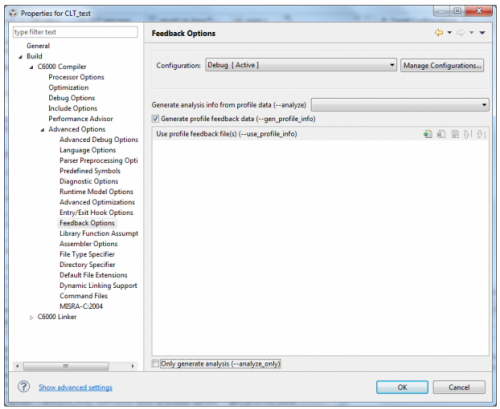

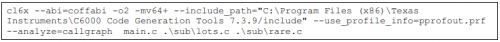

如果用户使用CCS编译工具,则需要在Build的属性里指定Feedback选项,然后正常编译即可生成携带分析代码的可执行文件。

Figure 4. CCS初编译的选项

2.获取分析信息

根据用户获取分析数据的不同,这里有两种方法,第一种方法适用于持续运行的程序,比如在基于SYS/BIOS的程序里,有些任务是以循环的方式存在的,这时用户需要自己从DSP内存里读取分析数据。

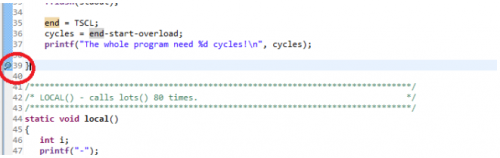

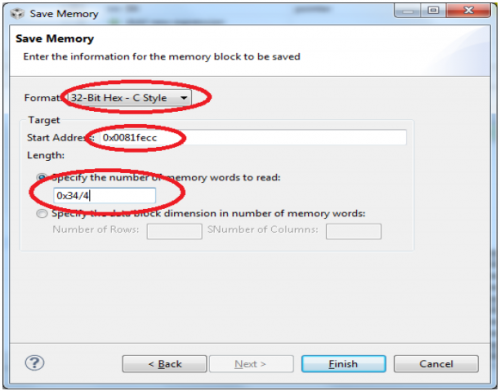

首先打开map文件,可以找到.ppdata段的内存地址,这个地址就是profile信息存放处,在例子中

ppdata 0 0081fecc 00000034 UNINITIALIZED ppdata段位于0x0081fecc这个地址,长度是34个byte。启动CCS,连接EVM板,下载out文件到DSP上,在main函数末尾加上调试断点,可以让程序到这里暂停(实际上,在用户代码中,可以把断点设置在需要的任何地方,profile的信息是实时更新的)。

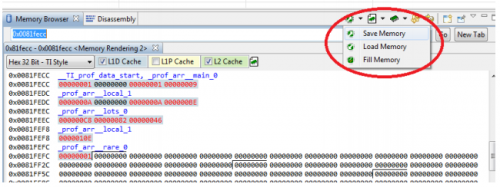

运行该程序,到达断点后,在View菜单里打开memory browser,将地址设定为0x0081fecc, 可以读到.ppdata 的信息,参考以下步骤将其存到工程目录下。

1)选取Save Memory

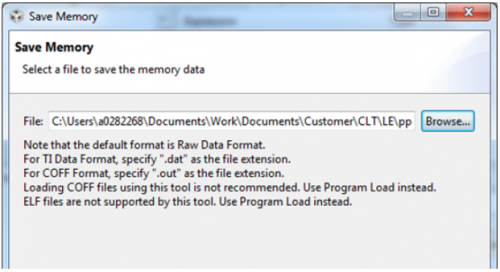

2)存放路径

3)确定数据地址和长度,如下图

4)修改dat文件

打开刚才存下的dat文件,注意到文件头的数据长度是以32比特字为单位的,我们需要以8比特字节为单位,如

1651 9 81fecc 0 d 1

修改为

1651 9 81fecc 0 34 1

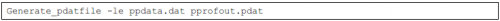

5)转换文件格式

对刚才的运行profile信息进行分析,得到优化后的cmd 内存排布文件,该文件内容如下,用户可根据自己的程序进行修改

如果是大端,则将-le选项改为-be选项。

第二种方法,针对于只需运行一次流程的程序,CCS可以自动生成pdat文件,需要注意的是,生成pdat文件的分析代码是在用户程序结束也就是exit()程序执行时进行,因此用户要保证自己的程序能完整运行到主函数出口结束,否则无法生成pdat文件,需要用第一种方法来获取数据。

3.重新编译代码

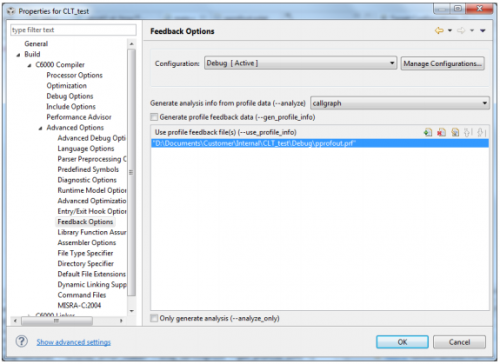

首先使用pdd6x从数据文件里提取prf文件作为重编译的输入文件

在命令行形式下,可以以以下形式调用输入文件生成csv文件,

在CCS环境下,只需要在CCS里指定需要的数据文件后产生csv文件,

Figure 5.CCS重编译的选项

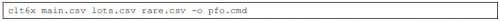

通过调用clt6x生成内存排布

将输出的pfo.cmd加入到项目的cmd文件重新编译输出优化后的out文件,cache优化到此完成。对比优化结果,对于TCP/IP的例子应用上,CLT带来了接近20%的提升,对于视频编码等应用CLT也带来了5%左右的提升。而且,用户代码量越大,则CLT可能带来的提升越明显。

4.结论

通过使用CLT工具,可以方便快捷的对用户代码的Cache 分配进行优化,用户不需要了解DSP Cache分配的详细信息,只需要在Simulator或者硬件板卡上运行定制的代码,就可以方便快捷地得到Cache的详细信息,并自动根据这些信息对程序在内存的分布进行配置已达到提升性能的效果。

参考文献

1.TMS320C66x DSP CorePac User Guide(SPRUGW0)

2.KeyStone Architecture Multicore Shared Memory Controller(MSMC)User Guide(SPRUGW7)

3.KeyStone Architecture DDR3 Memory Controller User Guide(SPRUGV8)

4.Cache Layout Tools Example

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 让DSP成为创新的不竭源泉(03-08)

- TMS320F2812慢速外设接口的时序控制(05-17)

- 在VC++中用ActiveX控件实现与单片机的串行通信(07-31)

- Whirlpool 选择赛普拉斯PSoC CapSense界面为其新型洗衣机产品实施触摸感应操控(03-24)

- MEGACHIPS采用SpringSoft CERTITUDE系统执行LSI验证(02-01)