金属eFuse内部结构揭密,不只是英特尔的专利

为了瞭解晶片如何制造以及为什么在某些情况下表现出特定结构,TechInsights经常针对晶片进行反向工程。本文讨论在金属闸逻辑制程中所采用的两种电子熔丝(eFuse)结构,包括英特尔(Intel)与台积电(TSMC)所打造的eFuse结构。

首先观察英特尔采用32nm高介电常数金属闸(HKMG)制程的Westmere/Clarkdale处理器(约2009年发表)中的eFuse结构。当时,英特尔采用eFuse作为一次性可编程唯读记忆体(OTP-ROM)的一部份。如今,我们知道其用途还包括保存编程程式码、晶片上配置资料以及加密密钥。

在金属闸极出现以前,电子可熔断晶片熔丝通常由多晶矽闸极层制造。但随着金属闸极CMOS制程出现,多晶矽无法再做为熔丝元件。那该怎么办呢?

英特尔在2010年发表了一份关于其32nm制程OTP-ROM的文件(Kulkarni et al. J. Solid-State Circuits 2010),透露其采用电子熔断金属熔丝(eFuse)作为记忆体元件。该熔断元件透过第2个过孔(via 2)连接第2层金属(metal 2;M2)汇流排到第3层金属(metal 3;M3)线制造而成。其3D热建模显示在过孔上面的部份是可熔断的元件。

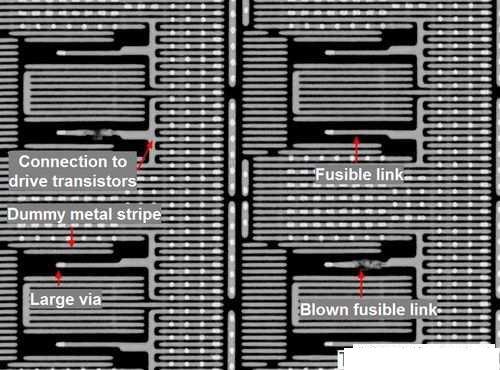

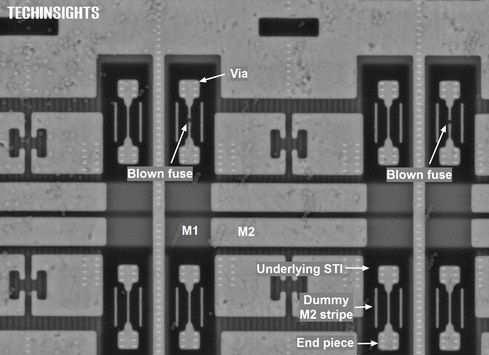

但是,我们发现在Westmere/Clarkdale处理器中的熔线(fusible link)或熔丝,采用如图1的顶层金属(metal 1;M1)走线建置。

图1:由图中可看到2个熔断的熔丝和6个完整的熔丝,彼此互连至基本的驱动电晶体。熔丝的熔断部份形状并不规则,但与构成M1走线的铜原子电迁移(EM)保持一致

英特尔所发表的论文中描述这种空隙的形成(熔断作用)是根据热辅助电迁移而来。

在熔丝的左侧可看到较大的过孔,这主要用于在过孔底部保持低电流密度,以确保这种电迁移空隙出现在熔线上。

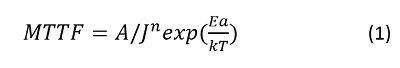

进行电迁移的金属线‘平均无故障时间’(MTTF)可由Black的公式(1)(JEDEC JESD63,1998)计算出来:

公式(1)中的J是电流密度,T为温度,Ea是指大约0.9电子伏特(eV)的活化能量(activation energy),A是常数,k是波兹曼(Boltzman)常数,n则是范围从1到2之间的建模参数,在此取n=1。

我们可以使用公式(1)估计英特尔的eFuse需要多长时间进行熔断。为此,我们测量了熔丝的截面积(1x10-10cm2),估算出MOS驱动电晶体约使用12mA的恒定驱动电流熔断熔丝(~1.2x108A/cm2)。根据现有的资料显示,在温度300℃、1.5mA/cm2的偏置电流下,Damascene镶嵌铜线的MTTF约为440小时(R. L. de Orio et al. VLSI-SoC conference 2009)。440小时MTTF是从其图表之一推论而来,很可能导致相当程度的不确定性。

根据英特尔的论文显示其熔丝在过孔顶部具有温度高达1,000 ℃的热点,但Westmere/Clarkdale eFuse采用像M1的金属片建置。我们怀疑M1熔丝可自加热至1,000 ℃,不过500 ℃也还算合理。这种假设结合公式(1)可实现约0.2微秒(us)的MTTF时间。英特尔使用约1us的时间偏置2V脉冲熔断其熔丝,因此,我们估计约0.2us的结果也很合理。

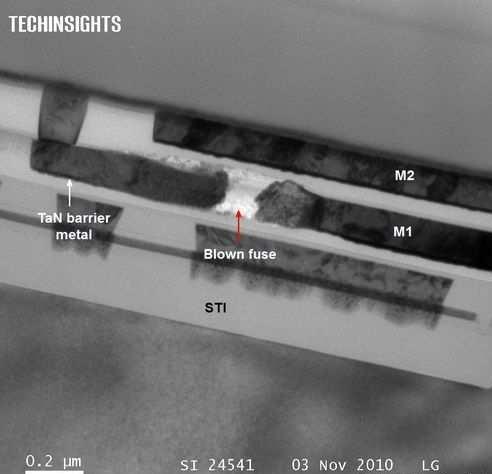

我们以库存的一款Westmere/Clarkerdale处理器复制了英特尔的熔丝熔断过程,并以图2显示熔断熔线的穿透式电子显镜(TEM)截面图。透过为此特定样本进行脱层后,暴露出接触M1熔线的M2走线。这些走线连接至一款4点探针,并施加0-2V偏置脉冲与13mA峰值电流。出现在M1走线的空隙表示成功熔断了熔丝。

图2:透过为此样本进行脱层后,暴露出接触M1熔线的M2走线。这些走线连接至一款4点探针,并施加0-2V偏置脉冲与13mA峰值电流。在M1走线的空隙表示成功熔断了熔丝

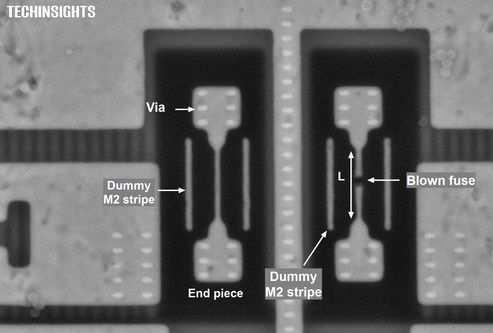

并不是只有英特尔一家公司采用eFuse结构,我们发现该元件也出现在台积电20nm平面HKMG制程的几款产品中。图3显示台积电的熔丝在M2时形成,其中两款已经熔断。这些熔丝成对地出现,其中之一可作为熔线,另一款则可能用于差动感测电路的参考元件。

图3:采用台积电eFuse 20nm平面HKMG制程的高通(Qualcomm) Gobi MDM9235数据机逻辑结构分析

图4所示的熔丝具有蝴蝶结形状的狭窄熔线,连接至更宽的转换区与较大的终端元件。图中可看到6个过孔接触至终端元件,过孔冗余提供低电阻连接至熔线。

图4:台积电的eFuse的放大图

较大的端点也可以作为散热片,让熔丝在熔断过程中两端较中间区域冷。熔线的中间部份理应是最热的部份,因为它距离冷却端点最远。这或许可解释为什么我们看到熔丝的熔断部份总是在中间,而非接近任一端点处。

我们可以估算出台积电eFuse的中间部份有多热。首先,我们假设在熔断过程中并未对端点元件加热,由熔线而来的热会流至端点元件,但不至于流进周围的电介质。这并不至于不合理,因为铜的热导率大约比熔线周围的低k电介质更好1,000倍(铜:385w/mK;SiOC:~0.4W/mK)。我们还假设在此计算中,铜的电阻率并不会随温度改变而发生变化。其实这项假设是错误的,但可大幅简化我们的计算。我们估计熔线中间部份的温度大约上升了:

- 英特尔将凌动处理器平台扩展至家庭和小型办公存储设备(02-11)

- 创新引领英特尔下一代数据中心建设(06-08)

- 谷歌叫板英特尔 自行设计ARM架构服务器处理器(11-17)

- Atmel携手英特尔应用EPID技术(07-24)

- 英特尔加快人工智能步伐,至强融核系列能担当重任?(06-18)

- 多核处理器构架的高速JPEG解码算法(02-07)