TMS320C6678存储器访问性能

摘要

TMS320C6678 有8 个C66x核,典型速度是1GHz,每个核有 32KB L1D SRAM,32KB L1P SRAM和512KB LL2 SRAM;所有 DSP核共享4MB SL2 SRAM。一个64-bit 1333MTS DDR3 SDRAM接口可以支持8GB外部扩展存储器。

存储器访问性能对DSP上运行的软件是非常关键的。在C6678 DSP上,所有的主模块,包括多个DSP核和多个DMA都可以访问所有的存储器。

每个DSP核每个时钟周期都可以执行最多128 bits的load或store操作。在1GHz的时钟频率下,DSP核访问L1D SRAM的带宽可以达到16GB/S。

DSP的内部总线交换网络,TeraNet,提供了C66x核(包括其本地存储器),外部存储器,EDMA控制器,和片上外设之间的互连总共有10个EDMA传输控制器可以被配置起来同时执行任意存储器之间的数据传输。

本文为设计人员提供存储器访问性能评估的基本信息;提供各种操作条件下的性能测试数据;还探讨了影响存储器访问性能的一些因素。

1. 存储器系统简介

TMS320C6678有8个C66x核,每个核有:

32KB L1D(Level 1 Data) SRAM,它和DSP核运行在相同的速度上,可以被用作普通的数据存储器或数据cache。 32KB L1P(Level 1 Program) SRAM,它和DSP核运行在相同的速度上,可以被用作普通的程序存储器或程序cache。 512KB LL2(Local Level 2)SRAM,它的运行速度是DSP核的一半,可以被用作普通存储器或cache,既可以存放数据也可以存放程序。所有DSP核共享4MB SL2(Shared Level 2)SRAM,它的运行速度是DSP核的一半,既可以存放数据也可以存放程序。TMS320C6678集成一个64-bit 1333MTS DDR3 SDRAM接口,可以支持8GB外部扩展存储器,既可以存放数据也可以存放程序。它的总线宽度也可以被配置成32bits或16bits。

存储器访问性能对DSP上软件运行的效率是非常关键的。在C6678 DSP上,所有的主模块,包括多个DSP核和多个DMA都可以访问所有的存储器。

每个DSP核每个时钟周期都可以执行最多128 bits 的load 或store操作。在1GHz的时钟频率下,DSP核访问L1D SRAM 的带宽可以达到16GB/S。当访问二级(L2)存储器或外部存储器时,访问性能主要取决于访问的方式和cache。

每个DSP核有一个内部DMA (IDMA),在1GHz的时钟频率下,它能支持高达8GB/秒的传输。但IDMA只能访问L1和LL2以及配置寄存器,它不能访问外部存储器。

DSP的内部总线交换网络,TeraNet,提供了C66x核 (包括其本地存储器) ,外部存储器, EDMA控制器,和片上外设之间的互联。总共有10个EDMA传输控制器可以被配置起来同时执行任意存储器之间的数据传输。芯片内部有两个主要的TeraNet模块,一个用128 bit总线连接每个端点,速度是DSP 核频率的1/3,理论上,在1GHz的器件上每个端口支持 5.333GB/秒的带宽;另一个TeraNet内部总线交换网络用256 bit总线连接每个端点,速度是DSP核频率的1/2,理论上,在1GHz的器件上每个端口支持16GB/秒的带宽。

总共有10个EDMA传输控制器可以被配置起来同时执行任意存储器之间的数据传输。它们中的两个连接到256-bit, 1/2 DSP核速度的 TeraNet内部总线交换网络;另外8个连接到128-bit, 1/3 DSP核速度的TeraNet内部总线交换网络。

图1展示了TMS320C6678的存储器系统。总线上的数字代表它的宽度。大部分模块运行速度是DSP核时钟的1/n,DDR的典型速度是1333MTS(Million Transfer per Second)。

图1 TMS320C6678 存储器系统

本文为设计人员提供存储器访问性能评估的基本信息;提供各种操作条件下的性能测试数据;还探讨了影响存储器访问性能的一些因素。

本文对分析以下常见问题会有所帮助:

1. 应该用DSP核还是DMA来拷贝数据?

2. 一个频繁访问存储器的函数会消耗多少时钟周期?

3. 当多个主模块共享存储器时,对某个模块的性能会有多大的影响?

本文中的大部分数据是在C6678 EVM(EValuation Module)板上测试得到的,它上面有64-bit 1333MTS的DDR 存储器。

2. DSP核,EDMA3,IDMA拷贝数据的性能比较

数据拷贝的带宽由下面三个因素中最差的一个决定:

1. 总线带宽

2. 源端吞吐量

3. 目的端吞吐量

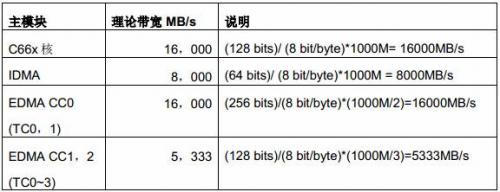

表1 总结了C6678 上C66x 核,IDMA 和EDMA 的理论带宽。

表1 1GHz C6678上C66x核,IDMA和EDMA的理论带宽

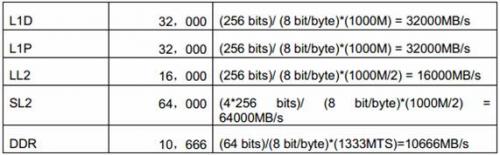

表2 总结了C6678 EVM(64-bit 1333MTS DDR)上各种存储器端口的理论带宽。

表2 1GHz C6678上各种存储器端口的理论带宽

表3 列出了在1GHz C6678 EVM(64-bit 1333MTS DDR)上,在不同情况下用EDMA,IDMA和DSP核做大块连续数据拷贝测得的吞吐量。

在这些测试中,L1上的测试数据块的大小是8KB;IDMA LL2->

TI DMA 存储器 TMS320C6678 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 让DSP成为创新的不竭源泉(03-08)

- TMS320F2812慢速外设接口的时序控制(05-17)

- 在VC++中用ActiveX控件实现与单片机的串行通信(07-31)

- Whirlpool 选择赛普拉斯PSoC CapSense界面为其新型洗衣机产品实施触摸感应操控(03-24)

- MEGACHIPS采用SpringSoft CERTITUDE系统执行LSI验证(02-01)