TI:PRU处理器开发详解

摘要

TI OMAPL13x, C674x, AM180x,OMAP-L137,C6747,AM170x等芯片上(本文统一以OMAP-L138代称)有一个PRUSS(Programmable Real time Unit Subsystem),可独立编程实现一些实时性要求高的个性化需求,实现产品的差异化。本文介绍PRU处理器架构,开发,调试方法。

PRUSS简介

在系统架构上,PRUSS是连接在OMAPL138内部总线SCR上的一个模块,与系统中其它主模块如ARM,DSP一样,可以访问芯片上的其它外设,工作在PLL0_SYSCLK2时钟域,即ARM/DSP 频率的一半。

图1 PRUSS框图

PRUSS包括两个PRU,通过自己的SCR与子系统的中断控制器、指令内存、数据内存、以及系统SCR相连。PRU不是一个加速器,它是32-bit Load/Store RISC架构小端处理器,每个PRU有32个通用寄存器R0~R31,4K byte指令RAM,512 byte数据RAM,指令RAM是独立的,互相之间不能访问,但数据RAM可以通过映射地址互相访问;专用的30个输入引脚和32个输出引脚(注:OMAPL137系列没有PRU外部引脚)。PRU没有Cache、指令流水线、及乘法指令。

1 PRU内存映射

1.1 指令空间

每个PRU独立的指令空间为0x00000000~0x00000FFF。指令空间由外部主处理ARM/DSP初始化,程序指针PC是32bit字地址,不是字节地址,如PC=2,代表指令地址0x08。

表1 PRU指令空间映射表

1.2 数据空间

每个PRU独立的512byte数据RAM空间为0x0000~0x01FF,因为数据RAM连接在PRU子系统的SCR上,所以子系统中的其它主模块也可以访问到这块空间,这段内存空间在另一个PRU 上的映射地址为0x2000~0x21FF。

位于数据空间的还有共用的中断控制器寄存器;PRU控制/状态寄存器,有各自的地址空间。

表2 PRUSS本地数据空间内存映射表

1.3 全局地址空间映射

PRU局部地址空间在系统全局地址空间映射端口为0x01C30000,如表3所示,PRU可以通过表2的局部地址,也可以通过表3的全局地址访问PRUSS的数据空间,通过全局地址空间访问要经过系统SCR2,比通过局部地址空间访问要慢。PRUSS外部主模块如ARM,DSP等可通过全局地址空间访问PRU资源。

表3 PRUSS全局空间内存映射表

2控制/状态寄存器

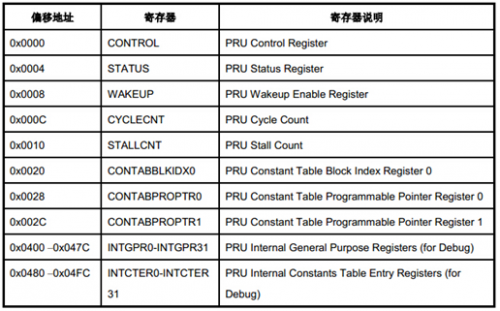

PRU0的控制/状态寄存器地址位于0x00007000~0x000077FF,PRU1的控制/状态寄存器地址位于0x00007800~0x00007FFF,寄存器列表如表4所示,各寄存器的详细说明请参阅[1] 。

表4 PRU控制/状态寄存器表

2.1 CONTROL控制寄存器

外部主模块ARM/DSP通过控制寄存器可以控制PRU的运行状态。

表5 PRU控制寄存器说明表

2.2 STATUS状态寄存器

状态寄存即PRU 的程序指针寄存器,与程序的真正运行状态有一个周期的延时。

2.3 WAKEUP唤醒使能寄存器

在程序执行SLP指令进入睡眠状态之前,使能WAKEUP寄存器相应的位,当输入状态寄存器R31相应的位置1时,即WAKEUP&R31!=0时,唤醒PRU。

2.4 CYCLECNT周期计数器

当CONTROL[ENABLE]=1和CONTROL[COUNTENABLE]=1时,CYCLECNT以PRU时钟周期计数。当CONTROL[ENABLE]=0或CONTROL[COUNTENABLE]=0时,计数停止。当重新使能时,恢复继续计数。

2.5 STALLCNT取指停止计数器

当CONTROL[ENABLE]=1和CONTROL[COUNTENABLE]=1,且由于某种原因PRU不能取指令时,STALLCNT开始以PRU时钟周期计数。其值总是小于,或等于CYCLECNT的值。

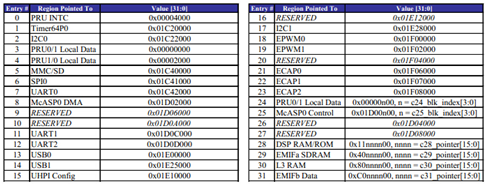

2.6 常量表

PRU提供32个常量地址表C0~C31,INTCTER0-INTCTER31是常量表的调试接口,当PRU停止时,外部主模块读取INTCTERn即得到常量表Cn的值。通过指令LBCO或SBCO从常量表指向的地址与寄存器之间以簇发方式传递数据。指令格式举例如下:

LBCO R2, C2, 5, 8 //从C2+5 的地址读取8 字节到R2, R3。

SBCO R2, C2, 5, 8 //将R2, R3 的数据写到C2+5 开始的地址。

表6 PRU常量表

在性能上与指令LBBO和SBBO没有区别,利用常量表可以节省通用寄存器的使用。

0~23号常量表提供的入口地址是固定的,24~31号常量表的域可通过寄存器编程设置:

2.7 INTGPR0~31调试通用寄存器

INTGPR0~31与通用寄存器R0~R31对应,为外部主模块提供一个调试窗口。当PRU停止时,ARM/DSP读/写INTGPR0~31直接读/写寄存器R0~R31。

3 PRU模块接口

3.1 PRU事件/状态寄存器R31

R31是一个特殊的寄存器,读与写操作时的功能是不一样的。

TI PRU 独立编程 OMAPL138 处理器 相关文章:

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 让DSP成为创新的不竭源泉(03-08)

- TMS320F2812慢速外设接口的时序控制(05-17)

- 在VC++中用ActiveX控件实现与单片机的串行通信(07-31)

- Whirlpool 选择赛普拉斯PSoC CapSense界面为其新型洗衣机产品实施触摸感应操控(03-24)

- MEGACHIPS采用SpringSoft CERTITUDE系统执行LSI验证(02-01)