QorIQ Qonverge B4860 SoC基带处理器深层剖析

QorIQ Qonverge B4860概述

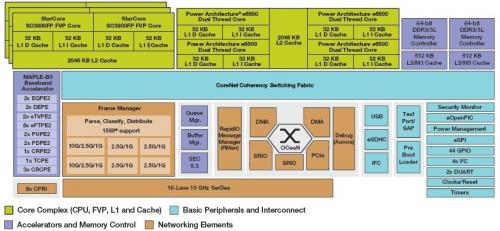

The QorIQ Qonverge B4860 device is a multistandard wireless base station system-on-chip (SoC) based on 28 nm process technology.The B4860 reduces overall power consumption for high-end wireless macro base stations to deliver the industry’s highest performance solution. The multicore SoC includes 10 programmable cores based on a StarCore flexible vector processor (FVP), 64-bit Power Architecture cores, as well as CoreNet and Multi-Accelerator Platform Engine (MAPLE)

technologies. The B4860 targets broadband wireless infrastructure and builds upon our proven success of existing multicore SoCs and DSPs in wireless infrastructure markets. The B4860 is designed to adapt to the rapidly changing and expanding standards of LTE (FDD and TDD), LTE-Advanced and WCDMA, as well as provide simultaneous support for multiple standards.

Layer 1 is implemented using a mix of StarCore SC3900FP high-performance FVP cores and the MAPLE baseband accelerator platform, which provides a highly efficient hardware implementation of standardized algorithms for each of the air interface standards in single and multi-mode operations. Layer 2 and transport processing are implemented using a mix of e6500 64-bit dual threaded Power Architecture cores, data path and security accelerators.

QorIQ Qonverge B4860框图

图1.QorIQ Qonverge B4860框图

The B4860 is perfectly suited to meet theperformance demands of wireless operatorsfor LTE, WCDMA and LTE-Advanced macrobase stations. It includes a combination of fullyprogrammable StarCore FVP cores, PowerArchitecture cores and powerful basebandacceleration to provide cost-effective, bestin-class performance, power efficiencyand connectivity. With four dual-threadede6500 64-bit cores operating at up to 1.8GHz and six SC3900FP DSP cores at up to1.2 GHz, the B4860 provides the requiredprogrammable performance. Additionally,the MAPLE hardware accelerators targetprocessing of baseband functions, such as FEC decoding and encoding, FFT, PDSCH and PUSCH embedded data flows, WCDMA chiprate and MiMO equalization, allowing base station manufacturers to deliver higher throughputs, lower latencies and better spectral efficiency.

While the four Power Architecture cores offer industry-leading processing capacity and a major leap in available processor performance for layer 2 and layer 3 in many throughput-intensive, packet-processing networking applications, raw CPU processing power is not enough to achieve multi-Gb/s data rates. To address this, the B4860 uses Freescale Data Path Acceleration Architecture (DPAA), which significantly reduces data plane instructions per packet and enables more CPU cycles to work on value-added services rather than repetitive low-level tasks. Combined with specialized accelerators for cryptography and pattern matching, the B4860 allows the user’s software to perform complex packet processing at high data rates.

The B4860 offloads performance and latencycritical layer 1 functions to MAPLE-B3, which integrates highly optimized and flexible accelerators. The smart partitioning introduced in B4860 provides an excellent balance between OEM intellectual property, hardwired accelerators and algorithms implemented on the fully programmable StarCore FVP and is highly efficient in terms of power dissipation and silicon area utilization.

QorIQ Qonverge B4860特性

硬件 Integrated processor cores and accelerators for layer control and transport processing Four e6500 dual-threaded, 64-bit Power Architecture cores Dual threading with

B4860 LTE-Advanced WCDMA QorIQ 相关文章: