100MHz 数字存储示波表样机的研究与试制----原理与主要指标

持式仪器中,一般都由信号调理、A/D转换器和高速存储单元组成,采样速率从20MSa/s到2.5GSa/s不等(FLUKE196为2.5GSa/s),通道数均为双通道,它们具有可靠性高、功能强等特点,其中,FLUKE190系列具有一定的分析功能。

Tektronix公司的高性能手持示波器产品均采用实时采样的方式实现,典型产品有THS700系列。带宽100MHz,采样率500MSa/S,具有示波器加万用表功能,其中THS720P还具有谐波分析功能。

1.4数字存储示波表的主要性能指标

本课题设计的数字存储示波表为双信号通道,一个外触发通道,100MHz带宽,最大存储深度为25K,设有光标自动测量功能,自动设置功能,峰值检测功能以及多种触发方式。

主要技术指标如下:

◆垂直分辨率:8bits

◆带宽fBW:双通道100MHz

◆垂直偏转系数:5mV/div-5V/div(1-2-5步进)

◆最大输入电压:40Vpp(1:1探头时)

◆上升/下降时间:≤3.5ns

◆上冲≤5%输入阻抗:1MΩ

◆最大实时采样速率:100MSPS

◆最大等效采样速率:5GSPS

◆存储深度:25KB/CH

◆时基范围:5ns/div-5s/diV(1-2-5步进)

主要功能指标有:

◇光标测量功能:用光标测量幅值域参数和时域参数。

◇滚动显示功能:在自动触发模式的慢时基档位下,屏幕处于滚动显示方式,波形从屏幕的左端滚动至右端。

◇存储回调功能:有菜单选择存储区域将屏幕上显示的波形或参数存储起来,菜单选择存储过的波形或参数回调出来。

◇反相功能:通过菜单选择把屏幕波形的极性取反。

◇自动量程和时基:对任一未知的信号,按示波器键盘上的"自动"键波形以适当的时基和量程显示在屏幕上。

◇触发特性:有内部/外部,上升和下降触发,触发方式有自动,正常,和单次,具有预触发功能。

◇ACQUIRE方式:有采样,峰值检测和平均三种捕捉方式;其中采样和峰值方式下用峰值显示,平均次数可选4/16/32/64/128次。

◇解析度:240点×320点,其中:纵向8.0格×25点(每1个点为1个象素),横向10格×25点(每1个点为1个象素)。

1.5本文设计的任务

数字系统设计是本项目的一个重要组成部分,而数据采集系统设计是其中的核心环节。本系统的设计是基于DSP+FPGA结构,利用FPGA极其灵活,可再编程的特点和DSP强大的数据处理能力完成数据的采集,缓存,处理,显示。在LCD显示方面,我们没采用一般的LCD控制器,而是利用FPGA丰富的资源生成LCD显示逻辑控制电路,外有两片SRAM进行来回切换向LCD送去数据显示。本论文就将围绕数字系统的设计而展开,重点对数据采集系统的硬件结构以及LCD显示电路进行介绍。

第二章数字系统总体结构

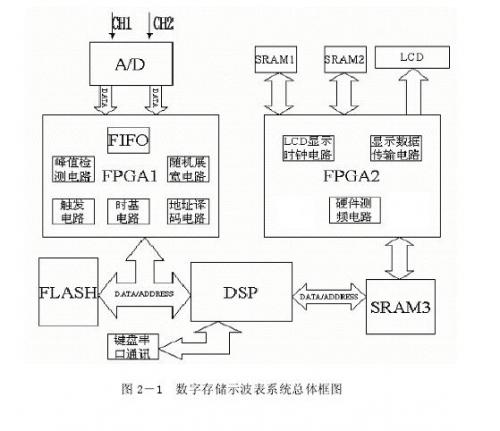

本数字系统采用的是FPGA+DSP结构。由于DSP和FPGA可以反复的实时更新程序和数字逻辑结构,所以这种结构具有很高的灵活性。系统的总体框图如图2-1所示:

FPGA(现场可编程门阵列)芯片是一种特殊的ASIC芯片,属于可编程逻辑器件,它是在PAL、GAL等逻辑器件的基础上发展起来的。同以往的PAL、GAL等相比较,FPGA规模比较大,适合于时序、组合等逻辑电路应用场合,它可以替代几十甚至上百块通用IC芯片。这样的FPGA芯片实际上就是一个子系统部件。这种芯片具有可编程性和实现方案容易改动的特点。由于芯片内部硬件连接关系的描述可以存放在磁盘、ROM、PROM或EPROM中,因此在可编程门阵列芯片及外围电路保持不动的情况下,换一片存储器芯片,就能实现一种新功能。可编程逻辑器件是一种用户根据需要而自行构造逻辑功能的数字集成电路。它的基本设计方法是借助于EDA软件,用原理图、状态机、布尔表达式、硬件描述语言等方法,生成相应的目标文件,最后再由编程器和下载电缆,用目标器件来实现。这种利用器件逻辑结构、由用户配置来实现任何组合逻辑和时序逻辑功能的器件,最初被视为分立逻辑电路中和小规模集成电路的替代物,随着设计技术和制造工艺的完善,器件性能、集成度、工作频率等指标不断提高,FPGA的应用范围越来越广,目前它已成为数字ASIC设计的主流。

如图2-1所示,本系统采用了两片FPGA.FPGA1采用ALTERA公司1K50系列的产品,它除了实现峰值检测、地址译码、触发、时基电路等功能外,而且由于系统采用了随机取样技术,所以计算触发脉冲到第一个取样脉冲时间间隔的随机展宽计数电路也做在了里面。同时,1K50内部有5KB的RAM.我们将它做成了两片容量分别为2.5KB的FIFO.这样,不仅节约了成本,而且还提高了速度。FPGA2采用了ALTERA公司1K30系列的产品,它主要产生LCD所需的时序以及控制显示数据的传输,同时还完成硬件测频的功能。DSP我们选用的是TI公司的TMS320VC5416.它是一种16位的定点DSP,采用了先进的增强型哈佛结构,片内共有8条总线(1条程序总线、3条数据存储器总线和4条地址总线)、专用硬件逻辑的CPU设计、片内存储器和在片外围电路等硬件,加上高度专业化的指令系统,使TMS320VC5416具有功耗小、高度并行等优点,可以满足实时处理的要求。它主要用来对采集进来的数据进行快速的处理、运算。

另外,FLASH用来存储DSP的程序代码、字库和一些需要保存的波形参数等;SRAM3用来保存DSP处理后的数据;SRAM1和SRAM2采用分时复用的方法来回切换读取SRAM3的数据,送到LCD显示。键盘控制与采集系统相对独立,所以我们选用了型号为AT89C2051的MCU,对每个键操作编写唯一的代码,然后通过串口送至DSP,由DSP对不同的键操作做出相应的处理。