一种使用USB对ADSP_TS101S进行链路口加载的方案

ADSP_TS101S(以下简称TS101)是美国ADI公司推出的TigerSHARC系列数字信号处理器中一款高性能的静态超标量处理器,它专为大规模信号处理任务和通信应用进行了结构上的优化,广泛应用于雷达等高速实时信号处理系统。

将程序代码加载到DSP内部程序空间时,通常采用开发器的JTAG接口将执行文件加载到DSP内存里进行调试;在硬件仿真完成后,又通过JTAG接口将生成的ldr文件烧写到与TS101相连的FLASH里固化。然而在很多情况下,使用开发器加载或固化程序很不方便,甚至无法实现,因此需要开发一种脱离开发器的TS101加载方式。基于这种需求,设计实现了基于USB总线的TS101链路口加载,只需一根USB线缆,即可实现TS1 01的程序在线重加载和固化。

1 Link Port协议

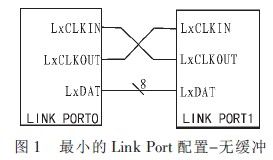

链路口(Link Port)是TS101的一种高速互联接口,它的通信是通过一个8位的数据总线和3个控制信号进行的,有4组LINK管脚。其中LxC LKIN和LxCLOUT是时钟/应答输入和输出管脚;LxDAT[7:0]-数据输入输出总线;LxDIR是LINK的方向指示信号。Link Port的最简单的连接方式(如图1所示)用了LxCLKIN,LxCLKOUT,和LxDAT。每个ADSP-TS101 DSP的LxCLKOUT与其它的LxCLKIN相连,两片TigerSHARC101 DSP芯片之间用LxDAT数据总线相连。

Link Port的最小传输单位是8个时钟周期,数据总量为4倍字长(16字节,在时钟的双沿触发)。传输被发送端初始化,只有当接收端设置LxCLKOUT(对于发送端为LxCLKIN)为高电平,发送才能被初始化为一次传输。LxCLKOUT为高电平意味着接收端为接收模式并且接收缓冲器为空。

2 TS101的软件设计流程及加载引导方式

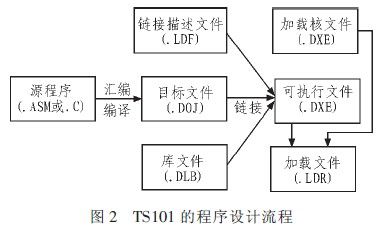

TS101的软件设计流程如图2所示。其中,链接描述文件(.LDF)定义了整个系统的存储器配置和程序中数据及代码的具体存放位置。加载核文件(.DXE)是指加载引导核程序,其大小为32 bit,放在加载文件的起始部分,其功能是用来实现TS101的正确引导。ADI公司在其DSP集成开发环境Visual DSP++安装目录的ldr子目录下提供了标准加载核文件及相应的源程序(.ASM)和链接描述文件。一般可直接使用提供的标准加载核文件或对其相应的源程序进行简单修改,重新编译链接生成所需的加载核文件。加载文件是由引导加载器(elfloader)将可执行文件进行一定的格式变化,并在起始位置附加上加载核文件生成的。

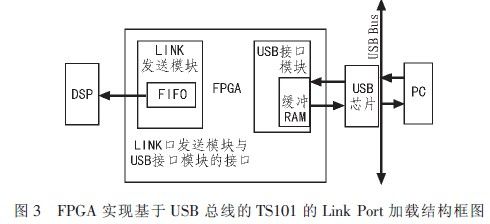

加载程序的外部设备可以直接向链路口缓冲写入数据,只要写入速率不超过DSP的主时钟频率即可。此处的外部设备采用计算机的USB总线。鉴于FPGA在数字电路系统设计中具有可靠性高、设计灵活、易于开发等优点,本文采用FPGA进行Link Port与USB的接口设计,使USB的输出满足Link Port的协议,以实现DSP的链路口加载。

3 USB总线及其与Link Port的接口

采用FPGA实现基于USB总线的TS101的Link Port加载结构框图如图3所示。

3.1 Link Port发送模块

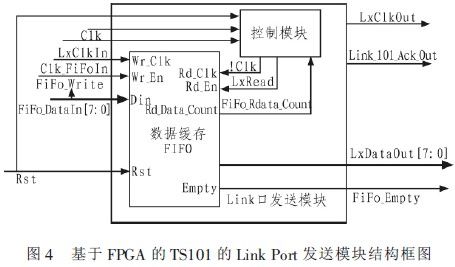

ADI公司网站上有推荐的实现TS101的Link Port收发协议的VHDL代码,但是比较复杂,鉴于本文只需要使用Link Port的发送功能,且无需缓冲,故根据图1所示的最小Link Port配置编写代码,实现Link Port发送功能。基于FPGA的TS101的Link Port发送模块结构框图如图4所示。

图4 中的FIFO负责对输出数据进行缓冲,当输入数据的速率高于Link Port时钟的频率时,Link Port的数据可以先存在FIFO数据中,当存入一定数量以后,再以Link Port的时钟把数据读出。当输入数据的速率低于Link Port的时钟数率的时候,Link Port的数据同样可以先存在FIFO中,当存入整数倍的4字数据量后,再以Link Port的时钟的数率发送出去。

图4中的控制模块是Link Port发送模块的关键模块,主要负责产生读FIFO的读使能信号和Link Port的发送时钟根据Link Port发送的时序特点,使用状态机来实现数据流的控制。当Link Port没有工作时,保持等待状态。需要传输数据时,首先检查LxCLKIN是否为高电平,若是,则说明接收端为接收模式并且接收缓冲器为空,可以初始化一次发送,否则要等待。开始传输数据时,数据首先被写入FIFO中,当判断到FIFO的输出信号EMPTY为高时,将处于默认高电平的LxCLKOUT信号拉低,在经过6个时钟周期的低电平后(在此期间检测LxCLKIN是否一直为高电平),LxCLKOUT拉高形成第一个LINK时钟上升沿,这个时候应该在数据线上产生FIFO内的第一个输出数据。LxCLKOUT下一周期拉低,第2个数据输出,这样经过16个时钟周期以后表示一次4字传输完毕。然后检测FIFO中剩余的数据FIFO_RDATA_COUNT,若大于4则继续上面的传输操作,否则,说明FIFO中只剩最后一个4字,这次传输LxCLKOUT的最后一个时钟上升沿产生以后,不再变低,一直保持高电平。然后,把本模块中的所有临时寄存器和FIFO复位。在产生完足够长度脉冲长度的清零信号后状态机重新进入等待状态。

3.2 USB接口模块

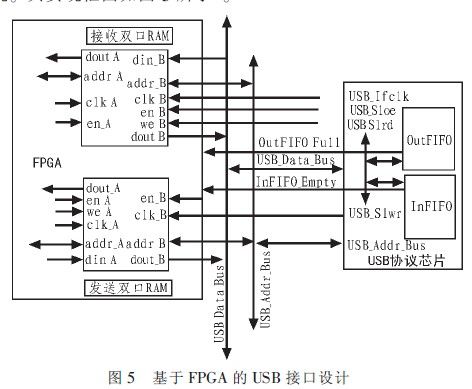

USB接口模块采用FPGA控制USB协议解析芯片来实现。其实现框图如图5所示。

本方案中,USB2.0协议解析芯片选用CYPRESS公司的CY7C68013A,它将一个USB外设所需的所有功能集成在一块芯片上。芯片提供了3种传输数据的方式,文中选择从FIFO(SlaveFIFO)模式。在SlaveFIFO模式下,8051微控制器不在数据的传输通路上,只负责设备的初始化和相应主机的控制传输请求,高速大批量的数据传输通过外部的主控者通过SlaveFIFO接口直接将数据填充到FX2LP的端点中(或者从里面读出),然后由硬件控制将数据传输给主机。

Slave FIFO的读写方式有两种:同步读写以IFCLK为时钟,IFCLK可以外部输入,也可以使用内部的30 MHz或者48 MHz时钟;异步读写时IFCLK信号无效,只需要提供读写信号即可进行数据读写。本文选择同步读写。

FPGA采用Xilinx公司的XC3S1000。FPGA在其内部建立2个双口RAM,来缓存收发数据;并与协议解析芯片的各控制信号相连,实现对其的读写控制。文中仅使用这个芯片的接收逻辑实现加载文件的USB总线传输,发送逻辑只用来做辅助调试和状态监测。

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)