破解市场迷思: MIPS? -最适用于设计MCU的处理器

图4:M4K PIC32与ST和NXP Cortex-M器件的CoreMark比较结果

工作在80MHz下的M4K PIC32采用2等待状态的存储器,其性能优于竞争对手的采用0等待状态存储器的Cortex-M3和M0器件,具体数据为:

比工作在120MHz下的STM32F高20% 比工作在72MHz下的STM32F高50% 比工作在100MHz下的LPC1768高31% 比工作在50MHz下的LPC1113高63%5. 低功耗与紧凑设计

典型SoC的大部分功耗和面积来自于处理器内核外部的存储器、外设和控制逻辑。然而MIPS科技明白,在单片机设计中,除了最佳的性能效率外,芯片成本和功耗也是产品取得成功的关键因素。MIPS在处理器内核设计中加入了特定功能,以最大程度地减少面积和功耗,本节将介绍其中一些功能。MIPS科技通过提供最佳的面积和功耗解决方案巩固了其在性能上的领先地位,具体内容将通过以下几节中M4K与Cortex-M3的比较结果为您展示。

5.1 低功耗特性M4K微架构的高性能允许应用工作于比其他内核更低的时钟频率。功耗与频率成正比,因此降低频率就是降低功耗。如前文所述,M4K内核的处理性能至少比Cortex-M3高20%,即功率效率(DMIPS/mw)更为出色,这意味着完成同一项作业需要的功耗更低。M4K内核的高性能有助于降低功耗,因为它可以更快地完成任务,从而有更多时间处于低功耗(空闲)状态下。

M4K内核是可综合设计,在不同低功耗工艺和物理库之间可任意移植。该内核是静态设计,允许时钟实时变化(需要时降至较低频率)。它甚至支持时钟停止,这会将功耗降至最低的uW级别(这种情况下的功耗主要取决于工艺上的漏电流)。

M4K内核提供多种功耗管理功能,通过使用微调时钟门控来控制动态功耗并支持掉电模式。M4K内核的大部分功耗来自于时钟逻辑和寄存器。在整个M4K内核中大量采用时钟门控,这可以提供一种有效的机制,即对于内核中的选定区域,当不使用时可将其关闭。M4K内核还提供一种机制,即使用内部寄存器通过特定WAIT指令控制内核进入低功耗和休眠模式。当执行WAIT指令时,内部时钟暂停,流水线冻结。任何中断或复位都将使内核退出休眠模式并恢复正常工作。

这些有效的功耗管理功能,连同低功耗设计工具的支持,都有助于显著降低动态功耗。与来自ARM网站的数据相比,在相似的配置和频率下,我们发现在采用180 nm制程时,M4K内核与Cortex-M3的动态功耗(mW/MHz)相似。

但采用90 nm制程时,工作在50 MHz且经面积优化的Cortex-M3的功耗为0.10 mW/MHz,额定功效为12.5(DMIPS/mW)。在相同的90 nm节点以及更高的200 MHz时钟频率和经面积优化的配置下,M4K的功耗仅为0.04 mW/MHz:与Cortex-M3相比,功耗降低60%,而功效是其2倍。

M4K内核在130 nm制程时显示出相似的低功耗特性。由于没有Cortex-M3在130 nm制程下的数据可供比较,因此下面我们只给出M4K在130 nm制程下的功耗数据:

在最大频率216 MHz以及经速度优化的配置下,功耗为0.17 mW/MHz 在100 MHz频率以及经面积优化的配置下,功耗为0.06 mW/MHz5.2 小尺寸特性

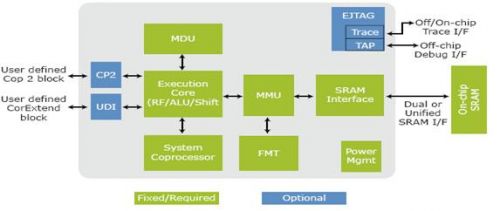

M4K内核是高效、高度可配置且灵活的处理器内核。图5显示了M4K内核中的可选模块,包括调试/跟踪(ETAG)、CP2协处理器接口和CorExtend扩展。MIPS16e ASE指令解码器是可选的。

图5:M4K内核框图

为减少门数规模,M4K内核提供了一组全面的配置选项。可配置选项包括使能/禁止调试功能、设置调试/跟踪断点的数量和类型、快速或慢速MDU、设置GPR寄存器的数量以及统一或合并数据和地址SRAM接口统一或分离。

这些配置选项综合用于实现速度或面积优化,以满足所需的应用目标频率,同时生成最小尺寸和最低门数。内核面积取决于工艺、单元库和目标性能。要对M4K与Cortex-M3在内核面积方面进行有意义的比较,应该考虑到这些因素。不过M4K内核的门数可低至33K,那么即便不考虑其功能多于Cortex-M3,M4K内核的尺寸仍比Cortex-M3小。

6. 生态系统SoC开发环境(包括硬件/软件调试工具和其他第三方解决方案)是处理器选型中的重要考虑因素。

MIPS科技拥有一个专门团队,提供一系列硬件和软件开发工具,帮助设计人员在SoC中成功集成和测试MIPS处理器内核,并在目标系统应用中验证其工作情况。这些工具包括System Navigator™ EJTAG仿真器、支持RTOS和Linux系统的GNU软件工具链、用于软件评估和协同模拟的周期精确与指令精确的模拟器、基于FPGA的开发/评估板和Navigator集成开发环境元件套件(ICS),以及基于Eclipse且与其他MIPS工具完全整合的开发环境。

图6:System Navigator调试探针和SEAD3开发板

此外,MIPS科技

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)

- ARM基础知识教程八(02-08)