破解市场迷思: MIPS? -最适用于设计MCU的处理器

,从而减少存储器转移开销并减少指令周期。这对增加计算吞吐量有着积极作用。

如前文所述,使用GPR作为影子寄存器可以减少服务中断(MCU系统中的常见事件)所产生的开销,从而提高系统性能。

当处理中断或异常时,M4K内核会决定使用哪个影子寄存器组并使其成为激活的GPR组,以允许中断向量继续执行。此过程完全不需要现场保护或恢复周期,因为指定的中断服务程序是当前激活的影子寄存器的唯一所有者。这意味着不仅在中断或异常代码实际开始执行前不会浪费时间,而且自上一次异常或中断事件激活以来的寄存器内容都会被保留。这会节省从SRAM空间重新获取特定值的时间。

3.4 MDU

M4K内核中的高性能MDU可在一个周期内完成一次32x16位乘法(或MAC指令)。在两个周期内完成32x32位乘法/MAC运算。

MDU有自己的专用功能单元,可独立于内核执行流水线进行工作。任何乘法/除法指令都会被送到MDU,这样内核流水线可并行处理其他操作,例如需要ALU、加载/存储和移位运算的指令。M4K内核中的MDU具有使信号处理运算加速的优势,例如FFT、FIR和IIR这些在工业和网络型应用中通常由单片机执行的滤波计算。以M4K加速DSP型函数的能力为例,PIC32在80MHz的频率下运行256点的16位radix-4 FFT运算需要22K个周期,共花费283ms,比基于Cortex-M3的单片机STM32少用14%的周期。

3.5 SRAM接口

访问代码和数据的速度快慢对处理器性能有明显影响。设计人员致力于设计一种存储器接口,使可用带宽最大化且最大程度地降低延迟,目标是实现0等待状态的数据传送。MIPS架构采用灵活的存储器总线结构,允许从高速闪存或高性能片上SRAM中执行代码。M4K内核集成了一个用于指令和数据存储器的高速、低延时SRAM接口。该接口支持单周期和多周期存储器访问。M4K SRAM接口可工作在双模式或统一模式下。双模式提供最高的性能,并具有控制数据(D-SRAM)和指令(I-SRAM)的独立总线。双模式允许在I-SRAM和D-SRAM接口上同时执行数据传输,以消除公用总线接口上可能产生的冲突现象。

I-SRAM接口能够重新定向信号输入,必要时允许将D-SRAM读周期重新定向到I侧。这样便可实现改良的哈佛架构(这是基于MCU的系统的常规特性),允许将非易失性数据存储在程序存储器中。

SRAM接口可在M4K内核的5级流水线中的任意位置中止指令事务。这样便可从外部系统控制器对外部事件(例如中断请求或通过EJTAG调试接口发出的请求)做出立即响应。在处理典型单片机应用的高决定性操作时,对外部中断事件的快速响应至关重要。

SRAM接口还可中止延时较长的数据传输。在处理典型单片机应用的高决定性操作时,对外部中断事件的快速响应至关重要。

M4K内核中的SRAM接口是一个高速、易用且可灵活配置的存储器接口,其中大多数传输可在一个时钟周期内完成。它除处理指令和数据存储器之外不会产生任何额外的协议或信号开销,这使芯片设计人员可充分利用M4K内核的最大性能。

Cortex-M3则没有如此全面的存储器控制功能,因此在性能上不如M4K内核。

3.6 CorExtend™

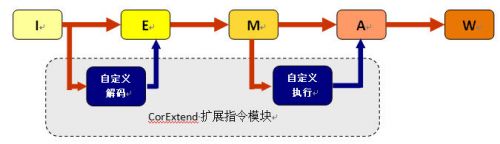

CorExtend是MIPS32架构的另一个独特功能,它为开发人员提供了产品差异化和定制功能。它是一个配置选项,通过用户定义指令(User Defined Instructions,UDI)与定制硬件的结合来扩展内核指令集。设计人员可通过CorExtend为内核增加功能,在目标应用中对成为瓶颈的特定应用功能进行加速,从而提高系统的整体性能。在典型MCU环境中,CorExtend可用于设计专用图形控制器、TCP/IP加速器、定制安全/加密逻辑、无线基带控制或其他实时控制接口等。CorExtend与内核流水线协同工作,如图3所示。CorExtend的功能与MIPS32完全兼容,并且所有领先的MIPS兼容开发工具均能支持。

图3:CorExtend流水线结构

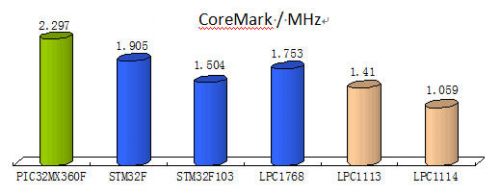

4. 性能基准测试

CoreMark是EEMBC开发的开源基准测试工具,专为测试处理器内核的性能而设计。CoreMark的架构可将处理器内核与任何相关系统隔离,包括存储器子系统的影响以及编译器可能使出的"优化把戏"。CoreMark可测试处理器流水线以及常用功能(包括读/写、整数和控制操作)的性能。因此,它提供的测试结果中的人为影响要比其他基准测试少,更接近处理器内核的真实性能。

源自CoreMark网站所述:"测试内容实际由多个常用算法组成,包括矩阵操作(允许使用MAC和常用数学运算)、链表操作(执行指针的常规用途)、状态机操作(数据相关分支的常规用途)以及循环冗余校验(CRC是嵌入式应用中很常用的功能)"。

图4比较了一些基于MIPS M4K和ARM Cortex-M3及M0的MCU的数据,这些数据取自CoreMark公开网站。

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)

- ARM基础知识教程八(02-08)