破解市场迷思: MIPS? -最适用于设计MCU的处理器

用作附加数据存储或者分配给专用向量中断控制器逻辑的"影子寄存器",在传统软硬件方法的基础上可显著减少中断延时和现场切换时间。

利用硬件乘除单元(Multiply Divide Unit,MDU)以及多个带符号/无符号乘法、除法和乘加(MAC)指令的软件支持,可有效提高MIPS32架构的信号处理性能。MIPS架构对MDU采用独立的流水线,使其可以与整数流水线并行工作。

2.2 比较MIPS与ARM的性能特点

以RISC技术为基础,并与可扩展的硬件和软件设计相结合,MIPS架构比ARM架构提供了更高性能、更低功耗和更为紧凑的设计。MIPS起源于高性能工作站和服务器的设计,而ARM的初衷是针对低端移动系统开发的基本内核。MIPS以其高性能产品的开发经验和设计优势进入主流嵌入式系统市场。而ARM传统架构中延续的种种方面限制其所能达到的性能等级,这使其与MIPS相比处于不利地位。

MIPS32 4K®处理器内核(包括MIPS32 M4K®内核)比同级的ARM Cortex-M系列内核的性能更加优良,应用程序的运行速度更快。一部分原因是采用了更高效的MIPS ISA和经过优化的软件工具,但主要原因是MIPS架构优越的设计功能,可实现更高的性能和执行效率,包括对单片机设计中实现的典型功能进行加速。例如:

MIPS内核包含32个GPR,而ARM内核只包含16个GPR。这减少了寄存器溢出,从而实现更高的性能。 MIPS内核包含影子寄存器组,而ARM内核不包含。使用影子寄存器可以加速中断处理的保存/恢复功能,从而使现场切换和中断延时占用更少的周期。 MIPS架构主要执行单操作指令,而ARM指令在写入GPR之前执行多次操作(例如,移位操作数、运算、检查条件位以及其他操作)。这使得MIPS可以更容易地达到较高的时钟频率。 与ARM相比,MIPS架构工作时采用的存储器寻址模式更简单,从而更容易达到较高的时钟工作频率。 MIPS架构的预测执行较少,这最大程度地降低了逻辑复杂性,并使MIPS内核可达到较高的频率。 M4K和M14K无需分支预测。而ARM内核采用复杂的分支预测逻辑。 MIPS架构实现了带延迟的分支,而ARM架构未实现,因此在短流水线设计时MIPS可实现更高的效率。 MIPS同时提供32位和64位架构,均可向下兼容并且更高性能的MIPS64也提供向下兼容。而ARM只提供32位架构,并且不是所有版本都支持向下兼容。3. 专为高性能MCU设计的处理器内核

在2002年,MIPS科技推出了M4K内核,这是一款高性能的综合性处理器内核,专为MCU和小尺寸嵌入式控制器设计而进行了优化。作为4K系列内核(已拥有超过120家被授权商)的成员之一,M4K已授权于近30家公司,其作为控制器而被广泛应用于移动手机、DTV、电缆调制解调器、GPS和数码相机系统中。此外,M4K内核在Microchip Technology的32位PIC32系列MCU产品中作为标准微控制器实现。

M4K内核的一系列设计功能提供了一流的性能,明显优于ARM Cortex-M系列处理器。

3.1 M4K执行流水线

M4K内核的性能可达到1.5 DMIPS/MHz,而按照ARM网站所列,Cortex-M3的性能只能达到1.25 DMIPS/MHz,大约比M4K低20%。(ARM Cortex-M0的性能甚至低至0.9 DMIPS/MHz,比MIPS32 M4K内核低40%。Cortex-M0还具有众多其他限制,我们将在后文介绍。)换句话说,Cortex-M3需要将时钟频率提高20%才能达到与M4K内核相同的性能,但这样做的后果是产生额外的功耗。

类似地,如第4节所述,M4K内核运行CoreMark基准测试的结果是2.297 CM/MHz,比同级的基于Cortex-M3的解决方案高出20-30%。MIPS注意到越来越多的人接受了CoreMark基准测试,因为与Dhrystone DMIPS相比,其对于CPU性能的测量更精确。

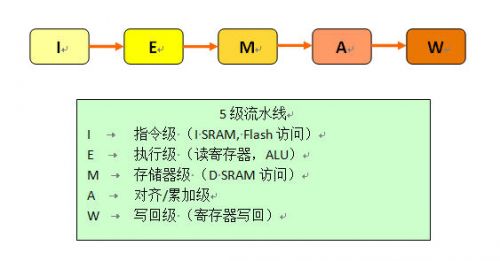

M4K的执行单元采用5级流水线微架构(如图2所示),而Cortex-M3内核的执行建立在3级流水线架构上。M4K内核的更深层流水线使其可工作于更高的最大时钟频率,这样每秒可处理更多指令,从而实现比Cortex-M3更高的性能和执行效率。

在M4K内核中,所有ALU和移位运算都在单个周期内完成。流水线中含有旁路逻辑,可提供对数据的快速访问,让数据在流水线执行完成前供下一个指令调用。这使得执行特定任务所需的周期数减少,因而性能得以提高。

图2:M4K内核5级流水线

3.2 系统协处理器(CP0)

系统协处理器(CP0)是MIPS架构所特有的,可以在M4K内核中找到。CP0作为辅助执行单元工作,可减少内核资源的某些管理操作(包括异常处理和存储器管理),从而提高内核性能。

3.3 通用寄存器(GPR)和影子寄存器

M4K内核提供一个配置选项,可将GPR的数量增加到最多16组,且每组都有完整的32个寄存器。这些GPR可在片上存储参数和操作数

- 基于ARM的除法运算优化策略(01-14)

- 基于ARM的CAN总线智能节点的设计(01-24)

- ARM基础知识教程五 (02-08)

- ARM基础知识教程六(02-08)

- ARM基础知识教程七(02-08)

- ARM基础知识教程八(02-08)