基于Blackfin处理器的网络视频服务器设计

概述

近年来,数字视频监控技术得到了越来越广泛的应用;同时,对视频图像的分辨率、压缩编码的实时性也提出了更高的要求。针对上述需求,本文介绍的网络视频服务器,采用ADI公司的Blackfin系列的高端BF561双核DSP芯片,完成了达到720×576 D1分辨率的PAL制视频信号的采集、MPEG-4格式压缩等运算量大及实时性要求高的功能,发挥了BF561双核处理器运算功能强大的优势。在处理压缩后视频码流的本地存储、网络传输等功能时又使用了BF537 DSP处理器;并且,在BF537处理器中选用了嵌入式uCLinux操作系统,更利于充分发挥网络视频服务器的文件系统操作和网络服务的效能。

系统设计

Blackfin系列DSP是ADI公司推出的专为满足目前音频、视频和通信应用等方面需求的嵌入式处理器,该系列DSP处理器在嵌入式网络多媒体中的应用有着显著的优点:性价比高、体积小、功耗低和外围接口电路设计简单。

ADSP-BF561处理器是Blackfin系列中的高性能产品,针对于多媒体和通信方面的各种应用。该器件的核心由两枚独立的Blackfin BF533 DSP处理器组成。这些Blackfin处理器将艺术级的dual-MAC处理引擎,简洁的RISC式微处理器指令集的优点,以及单指令多数据(SIMD)多媒体能力结合起来,形成了一套独特的指令集结构。ADSP-BF561集成了一套通用的数字图像处理外围设备,为数字图像处理和多媒体应用创建了一个完整的系统级片上解决方案[1]。

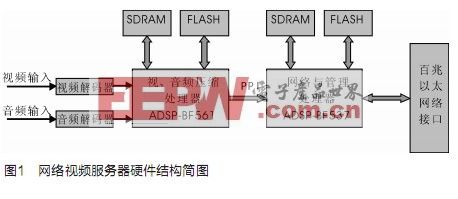

ADSP-BF537也是Blackfin系列家族中的一员,但其集成了ADSP-BF561处理器没有的网络接口,在网络视频服务器中很方便的完成网络功能。系统的硬件组成如图1所示。

ADSP-BF561和ADSP-BF537处理器在网络视频服务器中分别完成如下功能:

ADSP-BF561完成网络视频服务器视音频采集和MPEG-4视频压缩编码;

ADSP-BF537完成网络视频服务器网络接口、本地文件存储功能;

ADSP-BF561和ADSP-BF537处理器,都具有丰富的外部扩展接口。

ADSP BF561的视音频接口

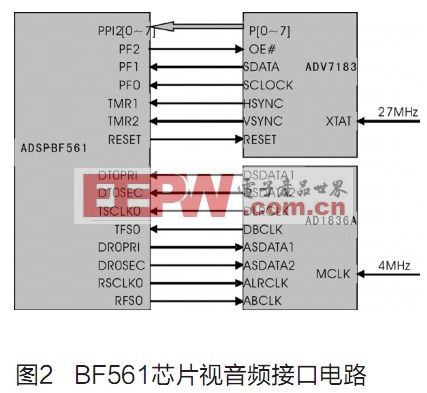

网络视频服务器的视频解码器采用ADI公司的专用视频解码芯片ADV7183;音频解码器同样采用ADI公司的音频解码芯片ADV1836A。

ADSP-BF561提供两个并行接口(PPI1和PPI2)。每个PPI接口包括一个专用时钟引脚,多达3个帧同步引脚和多达16个数据引脚。该PPI接口可以直接与并行A/D和D/A转换器、符合ITU-601/656标准的视频编码和解码器,以及其他通用外设连接。

通过BF561处理器的PPI外围接口电路,视频解码芯片ADV7183与BF561的并行PPI2接口连接,并且PPI2接口需要设置为专用的ITU-656模式;在ITU-R 656模式下,PPI2接口提供8或10位视频数据的接收和解析,支持内嵌导言控制信号和同步信号的片内解码。

ADSP-BF561提供2个双通道同步串行端口(SPORT0和SPORT1)来完成串行和多处理器的通信工作。SPORT有以下特点:支持I2S功能;每个SPORT都有2套独立的发送和接收引脚,支持8通道I2S立体声;每个端口都有一个数据寄存器,用以同其它部件间进行双向数据传输;每个发送或接收端口可以使用外部串行时钟或者使用自己产生的时钟;每个SPORT都可以自动发送和接收多个缓冲区的数据信息 [3]。

网络视频服务器中,音频解码芯片AD1836A则使用BF561处理器的其中一个SPORT端口连接,完成音频解码和传输操作。ADSP BF561的视音频接口电路如图2所示。

ADSP BF561的视音频压缩算法

网络视频服务器的视音频压缩算法采用ADI公司提供的MPEG-4 SP/ASP编码库实现。MPEG-4 SP/ASP是由ISO/IEC 14496-2描述的MPEG-4 的简单类(SP)和高级简单类(ASP)。其中,SP用于下一代便携式终端和窄带互联网。而ASP增加若干工具,编码效率提高了1.5~2倍;它们两个均在市场上获得越来越多的接受。该编码库提供一系列对Blackfin系列DSP的视音频编码的支持,可以在ADSP BF561上实现D1分辨率的实时视频图像的编码,并且支持完全动态的参数配置,用户可在系统运行时根据场景和网络带宽的变化改变编码的码率、帧率、关键帧间隔、量化值等等[4]。

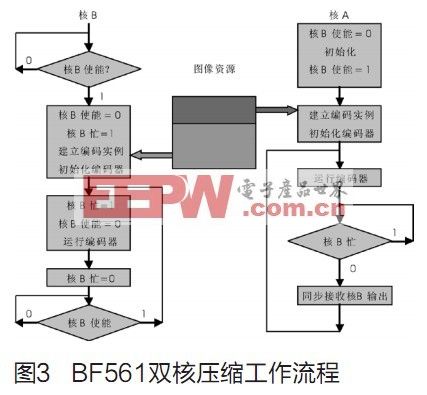

值得提出的是,对于双核的ADSP BF561处理器来说,在开发时需投入大量的精力进行两个处理器之间的任务调度和通信处理。而ADI公司提供的MPEG-4 SP/ASP编码库则提供了对ADSP BF561双核协同工作的支持,该视频编码库在调度ADSP BF561处理器的双核协同工作的流程如图3所示。

ADSP BF561在处理需要编码的图像资源时,双核之间可以采用采用对称负载模式和非对称负载两种模式进行;对称负载就是把需要压缩的视频图像平均分为上下两个半帧进行压缩(例如:PAL制D1图像分为720×288两个部分);本文采取的是非对称负载模式,如图3所示,这是由于核A还需要处理其

- 基于ADSP-BF537的视频SOC验证方案设计(05-18)

- BF51x树立数字信号处理器性价比新标杆(11-16)

- 用Blackfin处理器为您的应用置入低功耗引擎(01-11)

- 汇聚式处理器工业应用指南(09-11)

- 基于Blackfin 533 SPORTs口的USB主从接口设计(07-18)

- 基于ARM+uCLinux的网络控制系统设计与实现(05-03)