CPCI总线在数字化电台中的设计

时间:03-26

来源:今日电子

点击:

2 电源和地的连接

PCI2050使用的核心工作电压为+3.3V,CPCI标准机箱的底板上通过J1连接器提供满足要求的+3.3V电压,在使用时无须DC/DC转换。但根据标准设计规范,在PCI2050的电源引脚附近需要设置旁路电容。所以在印制电路板布线时,在PCI2050的所有电源引脚附近需要设置一个0.1μF的陶瓷电容器作为旁路电容。

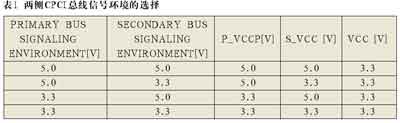

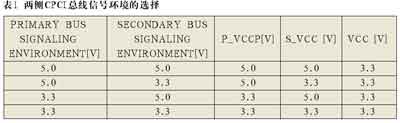

PCI2050在两侧总线方向都支持+5V和+3.3V信号环境,它们的选择是通过对P_VCC和S_VCC引脚施加不同的电压来实现的,详细的选择方式如表1所示。

由于PCI总线为高速总线,为了避免电源和地的干扰,在印制板布线时采取单独的电源层和地层布线。但因为在设计过程中使用了+5V和+3.3V两种电源,所以在同一电源层上又为+5V和+3.3V两部分分开铺铜。

3 PCI总线一次侧的连接

数字化短波电台的嵌入式计算机模块提供了符合PCI总线规范的标准PCI信号接口,这些信号与PCI2050的第一级总线侧的信号定义完全兼容,在设计时可以将嵌入式计算机的PCI信号输出直接连接到PCI2050一次侧的相应引脚。在初始化配置空间读写时,PCI2050作为上一级PCI总线的操作对象,提供了IDSEL引脚进行器件选择,按照PCI2050使用手册,该引脚可以连接到高24位PCI总线中的任意一根。同时,为了减低地址线的容性负载,需要在该信号连线上串接一个1kΩ的电阻。

在CPCI总线设计中,将PCI2050的IDSEL引脚通过1kΩ电阻连接到了AD19引脚。同样,PCI2050在二级总线侧可以支持9个PCI器件,对于每个二级总线侧的PCI器件的IDSEL引脚,也可以经过1kΩ电阻连接到PCI2050的S_AD31-S_AD16引脚中的任意一根。

4 PCI总线二次侧的连接

PCI总线信号经过桥接,在PCI2050的二级总线侧提供了标准的次级PCI总线接口信号,它们符合PCI总线规范的定义,同CPCI底板上的相应信号的定义也是相同的。但根据CPCI规范和PCI2050手册的要求,这些信号线需要经过适当的调理后才能与相应的CPCI J1、J2连接器的对应信号连接。

① 根据CPCI规范的要求,为了减小单板上的CPCI总线的信号线分支(stub)对总线的影响,必须对总线信号进行串联电阻匹配。PCB的布线特征阻抗应设计为65Ω±10%,匹配电阻阻值为10Ω。需要加串联匹配电阻的信号包括:AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#以及INTA#、INTB#、INTC#、INTD#。而且,从接插件J1或J2到PCI2050相应管脚,总的信号线长度要小于63.5mm(2.5英寸)。其中,从接插件插针到串联电阻的PCB连线长度小于15.2mm(0.6英寸)。所以,对上述信号在实际中使用10Ω排阻作为端接终端电阻进行串联的匹配。

② 在CPCI总线的设计中,对于GNT#0~GNT#6、REQ#0~REQ#6和二级时钟输出SCLKOUT0~SCLKOUT6等引脚根据CPCI规范对系统卡的要求,也需要加上相应的10Ω端接终端电阻。

③ 根据规范要求,对CPCI总线接口来说,对系统卡的一些PCI信号输出需要进行上拉,且上拉电阻必须被放置在端接终端电阻靠近CPCI J1、J2连接器的一侧上。可以在设计时对PCI2050的二级总线侧的相应信号通过8.2kΩ电阻上拉。需要上拉的电阻包括:FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#、INTA#、INTB#、INTC#、INTD#、GNT#0~GNT#9、REQ#0~REQ#9等。

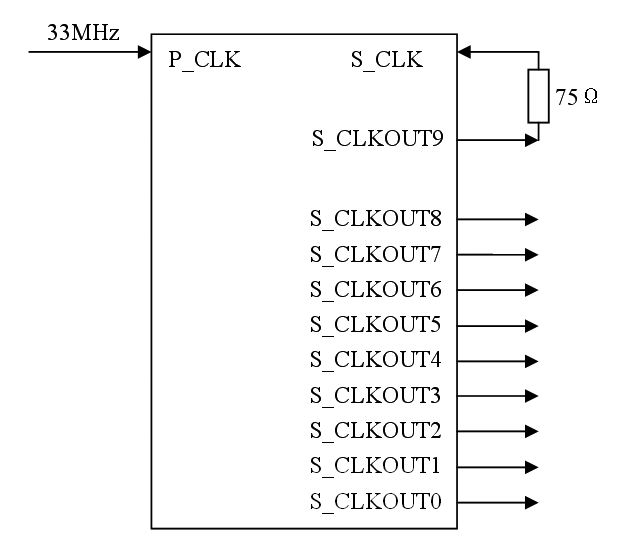

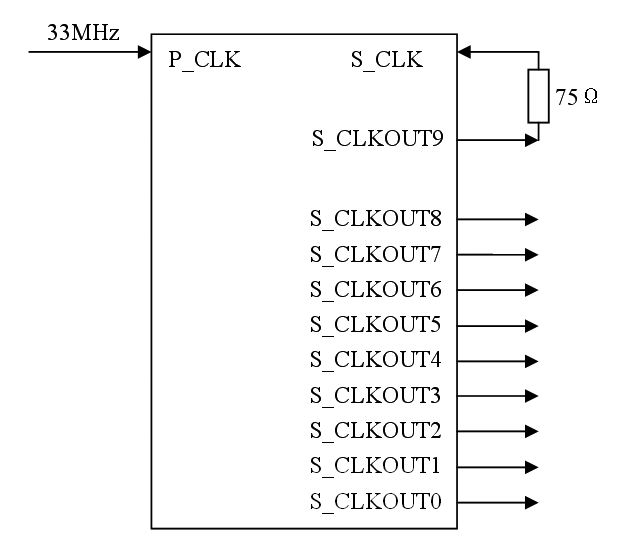

④ 对于二级时钟输出,PCI2050的二次侧有10个时钟输出S_CLKOUT[0..9],这些时钟输出可以通过相关寄存器分别使能。同时,为了保证PCI2050的二级PCI总线时钟和其他时钟输出同步,应将S_CLK引脚经一个75Ω电阻反馈到S_CLKOUT9引脚,如图1所示。

图1 PCI2050的时钟连接

⑤ PCI2050提供的JTAG边界扫描接口TDI、TDO、TMS、TCLK、TRST#,这些引脚可以与CPCI规范定义的J1连接器上的相应引脚直接连接。

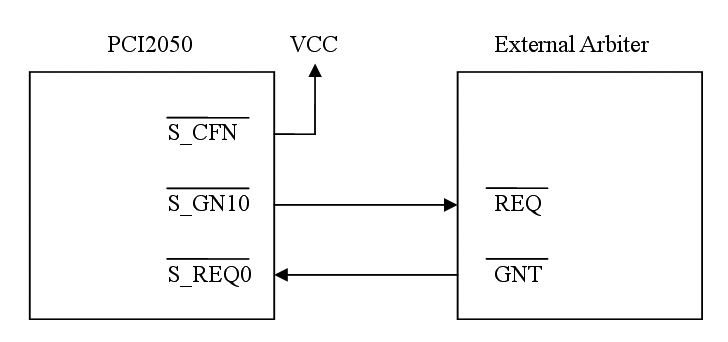

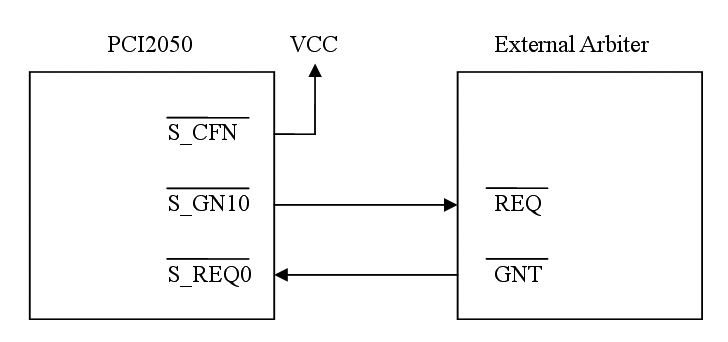

⑥ 对于二级总线的仲裁,PCI2050提供两种方式:外部总线仲裁和内部总线仲裁。S_CFN#引脚为选择引脚,当S_CFN#引脚为高时,使用外部总线仲裁器。这时,S_REQ#1~S_REQ#8和S_GNT#1~S_GNT#8引脚被置为高阻状态,外部仲裁器与PCI2050的连接方式如图2所示。

图2 PCI2050与外部仲裁器的连接

在PCI2050的内部总线仲裁模式中,S_CFN#引脚为低,PCI2050对外围卡通过S_REQ#0~S_REQ#8引脚提出的请求进行仲裁,然后通过S_GNT#0~S_GNT#8引脚和进行响应。PCI2050的S_REQ#0~S_REQ#8和S_GNT#0~S_GNT#8引脚分别与CPCI规范定义的CPCI J1、J2的相应引脚经过串接端接电阻和上拉后连接。

5 芯片工作模式的选

PCI2050使用的核心工作电压为+3.3V,CPCI标准机箱的底板上通过J1连接器提供满足要求的+3.3V电压,在使用时无须DC/DC转换。但根据标准设计规范,在PCI2050的电源引脚附近需要设置旁路电容。所以在印制电路板布线时,在PCI2050的所有电源引脚附近需要设置一个0.1μF的陶瓷电容器作为旁路电容。

PCI2050在两侧总线方向都支持+5V和+3.3V信号环境,它们的选择是通过对P_VCC和S_VCC引脚施加不同的电压来实现的,详细的选择方式如表1所示。

由于PCI总线为高速总线,为了避免电源和地的干扰,在印制板布线时采取单独的电源层和地层布线。但因为在设计过程中使用了+5V和+3.3V两种电源,所以在同一电源层上又为+5V和+3.3V两部分分开铺铜。

3 PCI总线一次侧的连接

数字化短波电台的嵌入式计算机模块提供了符合PCI总线规范的标准PCI信号接口,这些信号与PCI2050的第一级总线侧的信号定义完全兼容,在设计时可以将嵌入式计算机的PCI信号输出直接连接到PCI2050一次侧的相应引脚。在初始化配置空间读写时,PCI2050作为上一级PCI总线的操作对象,提供了IDSEL引脚进行器件选择,按照PCI2050使用手册,该引脚可以连接到高24位PCI总线中的任意一根。同时,为了减低地址线的容性负载,需要在该信号连线上串接一个1kΩ的电阻。

在CPCI总线设计中,将PCI2050的IDSEL引脚通过1kΩ电阻连接到了AD19引脚。同样,PCI2050在二级总线侧可以支持9个PCI器件,对于每个二级总线侧的PCI器件的IDSEL引脚,也可以经过1kΩ电阻连接到PCI2050的S_AD31-S_AD16引脚中的任意一根。

4 PCI总线二次侧的连接

PCI总线信号经过桥接,在PCI2050的二级总线侧提供了标准的次级PCI总线接口信号,它们符合PCI总线规范的定义,同CPCI底板上的相应信号的定义也是相同的。但根据CPCI规范和PCI2050手册的要求,这些信号线需要经过适当的调理后才能与相应的CPCI J1、J2连接器的对应信号连接。

① 根据CPCI规范的要求,为了减小单板上的CPCI总线的信号线分支(stub)对总线的影响,必须对总线信号进行串联电阻匹配。PCB的布线特征阻抗应设计为65Ω±10%,匹配电阻阻值为10Ω。需要加串联匹配电阻的信号包括:AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#以及INTA#、INTB#、INTC#、INTD#。而且,从接插件J1或J2到PCI2050相应管脚,总的信号线长度要小于63.5mm(2.5英寸)。其中,从接插件插针到串联电阻的PCB连线长度小于15.2mm(0.6英寸)。所以,对上述信号在实际中使用10Ω排阻作为端接终端电阻进行串联的匹配。

② 在CPCI总线的设计中,对于GNT#0~GNT#6、REQ#0~REQ#6和二级时钟输出SCLKOUT0~SCLKOUT6等引脚根据CPCI规范对系统卡的要求,也需要加上相应的10Ω端接终端电阻。

③ 根据规范要求,对CPCI总线接口来说,对系统卡的一些PCI信号输出需要进行上拉,且上拉电阻必须被放置在端接终端电阻靠近CPCI J1、J2连接器的一侧上。可以在设计时对PCI2050的二级总线侧的相应信号通过8.2kΩ电阻上拉。需要上拉的电阻包括:FRAME#、IRDY#、TRDY#、STOP#、LOCK#、DEVSEL#、PERR#、SERR#、RST#、INTA#、INTB#、INTC#、INTD#、GNT#0~GNT#9、REQ#0~REQ#9等。

④ 对于二级时钟输出,PCI2050的二次侧有10个时钟输出S_CLKOUT[0..9],这些时钟输出可以通过相关寄存器分别使能。同时,为了保证PCI2050的二级PCI总线时钟和其他时钟输出同步,应将S_CLK引脚经一个75Ω电阻反馈到S_CLKOUT9引脚,如图1所示。

图1 PCI2050的时钟连接

⑤ PCI2050提供的JTAG边界扫描接口TDI、TDO、TMS、TCLK、TRST#,这些引脚可以与CPCI规范定义的J1连接器上的相应引脚直接连接。

⑥ 对于二级总线的仲裁,PCI2050提供两种方式:外部总线仲裁和内部总线仲裁。S_CFN#引脚为选择引脚,当S_CFN#引脚为高时,使用外部总线仲裁器。这时,S_REQ#1~S_REQ#8和S_GNT#1~S_GNT#8引脚被置为高阻状态,外部仲裁器与PCI2050的连接方式如图2所示。

图2 PCI2050与外部仲裁器的连接

在PCI2050的内部总线仲裁模式中,S_CFN#引脚为低,PCI2050对外围卡通过S_REQ#0~S_REQ#8引脚提出的请求进行仲裁,然后通过S_GNT#0~S_GNT#8引脚和进行响应。PCI2050的S_REQ#0~S_REQ#8和S_GNT#0~S_GNT#8引脚分别与CPCI规范定义的CPCI J1、J2的相应引脚经过串接端接电阻和上拉后连接。

5 芯片工作模式的选

- 基于cPCI总线的嵌入式遥测前端处理器系统设计(04-27)

- 嵌入式系统的PCI接口设计(11-18)

- cPCI台热切换原理和实现(01-23)

- 基于Wishbone片上总线的PCI Bridge核的研究和应(01-26)

- PCI接口扩展卡的快速开发方案(01-23)

- 基于PCI总线的通用网络协议实验平台(01-24)