一种结构简单的低压低功耗ALU单元设计

3. 电路分析和仿真结果

一些其他的全加器设计将用来和本文的全加器比较,因为设计的目标是降低电路的复杂性和提高电路的速度以及能量损耗的降低,所以主要关注于门数少并基于传送门的全加器之间的比较。已有的全加器总结如下表2。

在0.35um工艺下仿真一些10管的全加器的DC特性,其中Vdd为3.3v,反向器的(W/L)p=1.4um/0.35um 以及(W/L)n=0.7um/0.35um(table3)。另外,此电路在1.9v的电压下依然可以正确工作,这为进一步降低功耗提供了一个很好的途径。

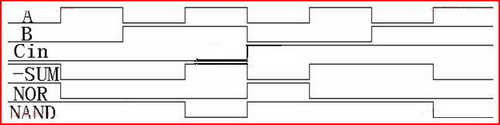

对整个电路进行DC分析,得到整个电路的功耗为12.12 uw,延时1.5ns,仿真结果见图5。另外在AC方面,这个电路的工作频率也是比较高的。

图5 . 电路仿真结果

4.结论

本文提出了一种新的1位的ALU单元。所提议的ALU单元在DC方面,可以在很低的工作电压下工作,功耗小且速度快;在AC方面,由于采用了CLRCL全加器可以工作在很高的频率下。同时,比较了现有的一些全加器的性能,可以看到文中的CLRCL电路不仅使用的晶体管的数目较少,同时它的功耗和速度性能也是比较优良的,极大的提高了1位ALU的性能。

本文创作者新点:

本文针对目前在RISC结构的MCU/MPU等中需要使用低功耗,小面积,快速的ALU单元,提出了一种新的结构简单的ALU单元结构,在此结构中使用的全加器是目前比较流行的10-T全加器,通过对全加器布尔逻辑的重组,使这种全加器在级连结构中不会产生多阀值损失的情况,最后在电路输出部分采用了电平恢复结构,使电路的输出波形很好,同时这种结构与现有的结构相比有着明显的面积,速度,功耗方面的优势。

参考文献:

[1] N.Zhuang and H. Wu,"A new design of the COMS full adder," IEEE J. of solid state circuits, Vlo.27,pp.840-844,May 1992.

[2] J.Wang, S.Fang, and W. Feng, "New efficient designs for XOR and XNOR function on the transistor level ,"IEEE J. Solid-State Circuits, Vol. 29, pp. 780-786, July 1994.

[3] R. Shalem, E . John, and L.K. John ,"A novel low-Power energy recovery full adder cell," in Proc. Great Lakes Symp. VLSI,pp.380-383, Feb.1999.

[4] Fartash Vasefi and Z. Abid ,"10-Transistor 1-bit Adders for n-bit Parallel Adders," IEEE J. of solid state circuit ,pp.7803-8656,Apr, 2004.

[5] H.T.Bui, A.K.Al-Sheraidah, and wang,"Design and analysis of 10-transistor full adders using novel XOR-XNOR gates," in Proc. Int. Conf. Signal Processing 2000(Wold Computer Congress),Beijing, China,Aug.2000

[6] N.Weste and K. Eshraghian, Principles of CMOS VLSI Design, a System Perspective. Reading, MA: Addison-Wesley,1993.

[7] Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang , Edwin Sha, and Jin-Gyun chung, "A Novel Mutipleser-Based Low-Power Full Adder," IEEE Transactions on circuits and systems-II: express briefs, Vol.51,No.7 ,July 2004.

[8] 卢君明,徐锋,胡鹏飞,"低电压低功耗全加器的研究设计,"固体电子学研究与进展,第24卷,第3期,2004年8月

[9] 张杰; 基于FPGA的八位RISC CPU的设计[J]; 微计算机信息,2006-35-05