ISO72x系列数字隔离器的高压使用寿命

工业控制系统通常使用数字隔离器,该系统停工期成本较高,且可靠性也是该市场设备提供商最为关注的问题。产品说明书规范涵盖了该隔离器的全面功能和参数性能,包括单事件、高压瞬态隔离层的最大电压能力。但是,这些规范均不足以应对长期高压应用条件下隔离特性的行为。

本应用报告提供了在 150℃ 结温下,ISO72x 系列数字隔离器与一个 560V 连续输入至输出一起运行时的隔离特性的长期预测。

本报告首先对绝缘特性和额定电压进行了定义,然后对 ISO72x 隔离层进行了描述。并显示了经时击穿 (TDDB) 模型和 ISO72x 测试结果。

2、绝缘特性与额定电压

物理及化学构成决定了介电层具有固有绝缘特性,其包括可能在生产过程中引入的杂质和非完整性物质(内含物)。人们非常清楚,这些内含物会导致该种绝缘特性会随时间而改变,并导致介电层的最终失效。可通过对介电层施加一个电场和/或通过提高其温度来加速这些变化的发生。

大多数数字耦合器的产品说明书规范均只包括初始额定电压。对于基本绝缘应用而言,大多数常见(包括 ISO72x 系列)隔离耦合器是指 4000-V (VIOTM) 额定电压。表 1 为厂商提供的典型的产品说明书额定电压。单独从这一方面来讲,该额定电压并不意味着这种产品可以无限期地或者在任意高温条件下经受 4000V 的电压。实际上,只有在该额定电压下才有可能预测这种产品随时间而变化的耐压特性,其耐压特性可能会受到如工厂地面环境不断的高压击打 (strike) 的影响。

人们所关心的另一个绝缘额定电压为工作电压 (VIORM),或连续运行电压。这种额定电压意味着,如果其运行在施加于输入端和输出端之间的电压下,那么该产品在整个使用寿命中均保留了其绝缘特性。通常,半导体产品的最短使用寿命为 10 年。

3、ISO72x 器件的描述

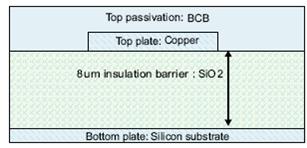

ISO72x 系列产品由一个被高阻抗隔离层分离的输入和输出半导体器件组成,而设计该高阻抗隔离层的目的是用于电子信号在该隔离层上的传输。ISO72x 使用容性耦合以实现在隔离层上传输信号,同时保持与输入相关的输出端隔离。该电容器介电层为半导体级二氧化硅,并且为隔离层。如图 1 所示,该电容器构建在一个由镀铜组成的顶板 (top plate),以及一个由掺杂硅基板制造而成的底板之上。顶板 BCB(苯并环丁烯)自旋对介电质的钝化增强了这种绝缘特性。

图 1、ISO72x 系列产品的隔离层 4、建模和测试方法

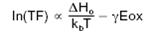

其中,?Ho 为氧化物击穿的热函(被称为活化能),Eox 为隔离层的电场,其由隔离层厚度外加应力电压 (VS) 的比率得出,kb 为波尔兹曼 (Boltzmann) 常数,而则为场加速参数。该数据是在?150℃ 最坏运行条件下得出的,以避免进行温度修正。由于 VS 与 Eox 成比例关系,且不必解决温度加速问题,因此可以使用一个简化模型(如方程式 2 所示),与此相对,只有 TF 加速完全应用了较高电压 VS。

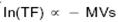

其中,M(电压加速参数)为一个与成比例关系的常数。因此,通过使用方程式 2,E-模型预测其为指数关系,或者,如果使用对数标尺将 TF 绘制在 Y 轴上,并使用线性刻度将 VS 绘制在 X 轴上,那么该关系看起来为线性图。既然这样,M 就为该条线的斜率。 |

方程式 1

方程式 1 方程式 2

方程式 2