基于FPGA的线阵CCD驱动器设计

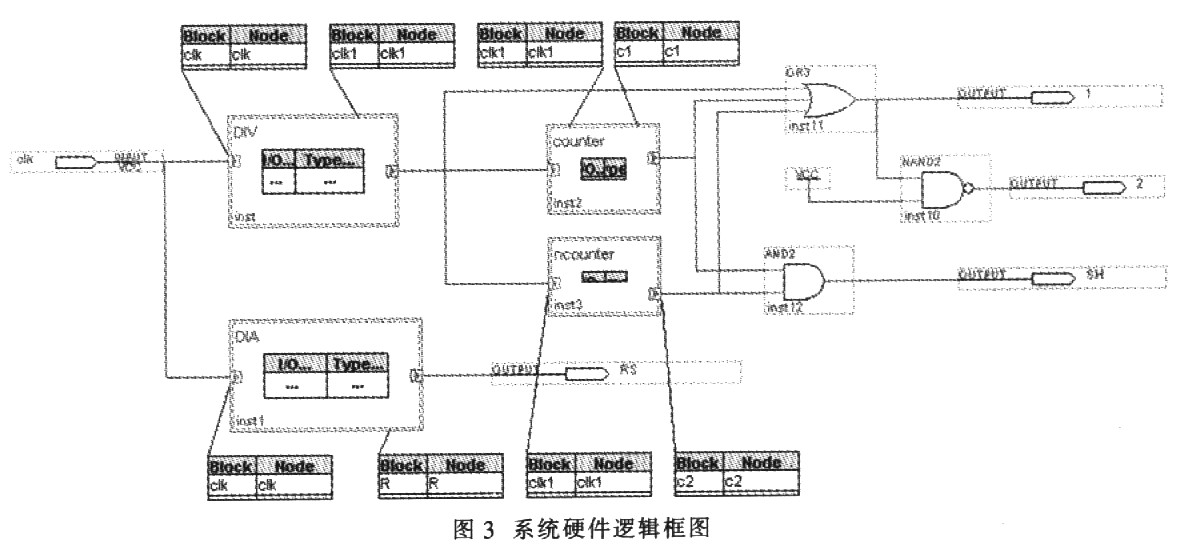

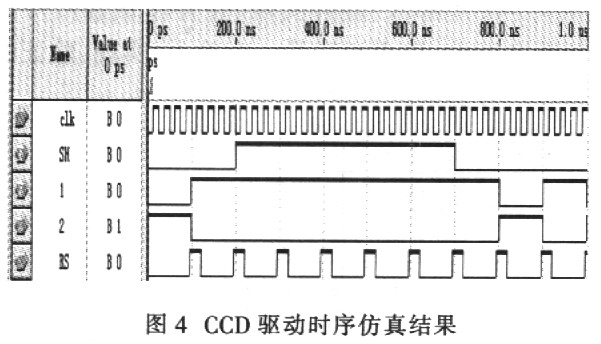

由TCDl208AP的时序图可以看出,TCDl208AP采用二相驱动脉冲工作,时序脉冲驱动电路提供4路工作脉冲,即光积分脉冲SH,电荷转移脉冲φ1、φ2,输出复位脉冲RS。系统提供的主时钟频率CLK为4 MHz,设定数据输出频率为1 MHz。TCDl208AP的典型最佳工作频率为l MHz,该器件具有2160位有效像元,正常工作时要有52个虚设单元输出(DUMMY 0UTPUTS)信号(含暗电流信号)。因为该器件是二列并行传输,所以在一个周期内至少要有1 106(2 212/2=1 106)个φ1脉冲,即TSH> 编译后,最后得到仿真的波形结果如图4所示。 5 结束语 本设计采用QUARTUSⅡ开发系统实现编程,完成了电路功能的设计、时序综合与分析及文本和图形输入,并根据工程需要将结果下载到Altera公司的Cyclone系列FPGA芯片EPlCl2Q240C8中产生CCD驱动时序,不但得到了良好的CCD输出效果,而且大大简化电路设计,提高可靠性,降低功耗,加快研发速度。