基于FPGA的电涡流缓速器控制系统

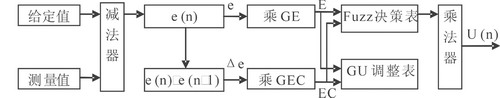

图2 模糊控制器原理图 从原理图可以看出,本模糊控制器采用了二维模糊调节的方式,以改善系统的动态性能,即模糊控制器的输入为给定值与测量值偏差e和偏差变化率芿=ek-ek-1所对应的两个模糊控制集,经量化因子量化后,得到对应的量化等级,其量化等级分别表示为{-7、-6、-5、-4、 -3、-2、-1、0、1、2、3、4、5、6、7}。控制决策表是经离线模糊控制推理运算,并结合系统的实际运行进行调整、修改得到的,但它仅反映常规模糊控制的控制规则,不能保证系统的动、静态特性在大范围内最优。因此,为改善模糊控制器的性能,根据系统的误差和误差变化等信息,对控制器实行在线调整,实际输出的控制量为决策表值与比例因子的乘积。比例因子的选取规则如下:当e和芿较大时,系统主要是减少误差,加快动态过程,应取较大值;当e和芿较小时,系统接近稳定值,应取较小值。最后,按此原则并结合实际经验得到比例因子表。

|

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)