基于FPGA和ARM的图像采集传输系统

图像处理技术的快速发展,使得图像采集处理系统在提高农业生产自动化程度中的应用越来越广泛。目前的图像采集系统有的基于CCD摄像机、图像采集卡和计算机,有的基于CCD摄像机、解码器、FPGA和DSP,而有的基于CMOS图像传感器芯片、FPGA和DSP,它们在实时性,灵活性,可维护性方面各有优缺点。而在农业生产中,以基于CCD摄像机、图像采集卡和计算机的系统居多。本文结合实际系统中的前端图像处理和图像数据传输需要.充分利用ARM的灵活性和FPGA的并行性特点,设计了一种基于ARM+FPGA的图像快速采集传输系统。所选的ARM (Ad-vanced RISC Machines)体系结构是32位嵌入式RISC微处理器结构,该微处理器拥有丰富的指令集且编程灵活。而FPGA(Field ProgrammableGate Array)则在速度和并行运算方面有很大优势,适合图像处理的实时性要求。本文选用Intel公司的Xcale PXA255和Xilinx公司的Spartan-3XC3S1000来实现本系统的设计。

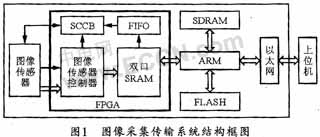

1 系统结构设计

本系统的结构框图如图1所示。图中,图像传感器模块负责图像采集,FPGA用来控制CMOS图像传感器芯片,ARM负责图像数据的交换、以太网芯片的控制及UDP/IP协议的实现,以太网模块主要实现以太网数据传输,SDRAM用于存储图像数据,FLASH为程序存储器。系统工作时,先由FPGA将CMOS传感器采集的数据存储到双口SRAM,再由ARM从FPGA的双口SRAM中读取数据并存储到SDRAM,存满一帧图像数据后,ARM便通过以太网芯片将数据发送给上位机。

|

2 系统硬件设计

2.1 CMOS图像传感器模块

本系统采用OV9650作为图像采集传感器。OV9650是Omni Vision公司的彩色CMOS图像传感器,可支持SXVGA,VGA,QVGA,QQVGA,CIF,QCIF,QQCIF模式和SCCB接口,并具有自动曝光控制、自动增益控制、自动白平衡、自动带通滤波、自动黑级校准等功能。OV9650的最大帧速率在VGA格式时为30 fps,在SXVGA格式时为15 fps。本系统采用VGA格式。

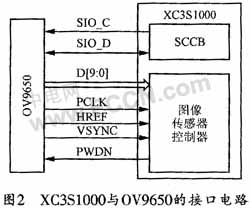

2.2 FPGA模块

FPGA主要用于图像传感器的控制、图像数据的缓存及外围芯片时序的产生。考虑到图像处理算法的实现需要,本系统选用了Xilinx公司的XC3S1000,它属于SPARTAN-3系列,容量为100万门。在本设计中,FPGA通常运行于80 MHz。XC3S1000与OV9650的接口电路示意图如图2所示。FPGA的内部结构包括CMOS控制单元、SC-CB接口单元、双口RAM单元、FIFO单元等。其中CMOS控制单元又包括帧同步模块、场同步模块、像素时钟模块等。

|

2.3 ARM处理器模块

本系统的ARM处理器选用PXA255,用于实现图像数据交换和以太网数据传输等功能。PXA255是Intel公司推出的基于第五代ARM RISC体系结构ARMV5TE的微处理器。CPU的运行频率最高为400 MHz,有32 KB指令Cache,32 KB数据Cache,2 KB微数Cache,并带有丰富的串行外设接口,并可支持各种存储器芯片。本系统采用两片SDRAM和两片FLASH存储器,其中SDRAM用于图像数据暂存,本系统选用SAMSUNG公司的K4S561632C-TC75,容量为32 MB。而FLASH程序存储器则选用Intel公司的E28F128J3A-150来作为NOR FLASH,容量为16 MB。

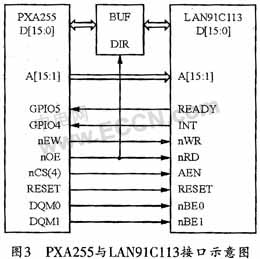

2.4 以太网传输模块

本系统的以太网芯片选用LAN91C113。这是SMSC公司推出的快速以太网10/100 Mbps控制器,支持多种嵌入式处理器主机接口。LAN91C1B内部有8 KB的FIFO,可用于接收和发送数据的存储。此外,LAN91C113芯片还集成了CSMA/CD协议的MAC(媒体访问控制层)和PHY(物理层),IEEE802.3/802.3u-100BASE-TX/10Base-T规范。本系统中,LAN91C113的串行EEPROM接口与AT93C46相连。PXA255访问LAN91C113采用异步静态存储器方式,LAN91C113的地址使能信号AEN与PXA255的静态芯片片选四相连。PXA255与LAN91C113接口示意图如图3所示。

|

3 系统主要模块的工作原理及实现

3.1 FPGA图像采集的实现

OV9650的数据输出采用Bayer原始数据输出格式,每个象素同时只输出一种颜色。奇数扫描行输出RGRG…,偶数扫描行输出GBGB…。FPGA负责图像传感器数据的采集。

上电后,系统首先对CMOS图像采集芯片进行初始化,以确定其工作模式。这些参数受OV9650内部相应寄存器值的控制。FPGA通过控制SCCB总线来完成参数的配置。

系统配置完毕后,便可进行图像数据的采集。图4和图5是数据采集与输出的时序图。其中VSYNC是场同步信号。HREF是水平同步信号。PCLK是象素数据输出同步信号。HREF为高时即可开始有效数据采集,而PCLK下降沿的到来则表明数据的产生,PCLK每出现一个下降沿,系统便传输一位数据。在HREF为高电平期间,系统共可传输640位数据。在一帧图像中,即VSYNC为低电平期间,HREF会出现480次高电平。而下一个VSYNC信号上升沿的到来则表明分辨率640×480的图像采集过程的结束。

- 一种基于FPGA的接口电路设计(11-18)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- 设计性能:物理综合与优化(04-28)

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 采用灵活的汽车FPGA 提高片上系统级集成和降低物料成本(04-28)

- 面向 FPGA 的 ESL 工具(04-29)