基于AD7864和DSP的4路数据采集系统

在阵列信号处理中,往往需要对多个阵元同时进行采样,以保留接收到的各路信号之间的相位信息。对于一个四元十字阵,就需要对4路信号同时进行采样,以便在随后的处理中解算出各路信号之间的时延关系。在这个过程中,高速率和高精度的A/D转换就显得尤为重要,它直接影响着随后的数字处理结果的精度。AD7864是一种高速、低功耗、可以4通道同时采样的A/D转换器。它的主要特性有:高速12位A/D转换器;同时采样4个输入通道,并具有4个采样、保持放大器;0.35ms采样保持获取时间,每一个通道转换时间1.65ms;可以通过软件或者硬件的方法选取用于采样的通道;单电源供电(+5V);多个转换电压范围;具有高速并行接口,可以与处理器直接连接;低功耗,每通道功耗90mW;对于每一个模拟输入通道均有过压保护电路。AD7864 4通道同时工作时,最大采样率可以高达130KHz。

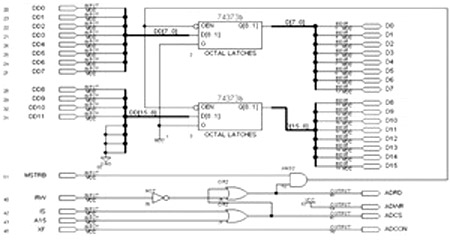

DSP与AD7864的接口电路

AD7864具有片内时钟、读写允许逻辑、多种通道选择方式以及内部精确的2.5V参考电压,这使得其与高速处理器的接口变得非常简单。考虑到实际工程中要求的工作电压、转换精度以及系统硬件设计的便

利等因素,在硬件系统中选用AD7864-1。DSP选用TI公司的TMS320C5409。

AD7864转换后的数据读取有两种方法,即转换中读取数据和转换后读取数据。转换中读取数据是在下一个通道转换结束之前读取前一个通道的数据。转换后读取数据是在全部通道均转换结束后,才读取数据。在此硬件系统中,采用转换后读取数据的方式。其具体工作过程如下:

当转换起始信号有效时(上升沿),所有采样保持器进入保持状态,开始对选择的通道采样。Busy输出信号在转换起始信号上升沿时被触发为高电平,并在转换过程中一直保持为高,当全部通道转换结束后,才变为低电平。转换结束信号在被选择的通道中每一个通道转换结束时均有效。各个通道转换后的数据保存在AD7864内部相应的锁存器中。所有通道转换结束后,当读信号和片选信号有效时,就可以并行地从数据总线上读取数据。数据读取时,按照转换顺序进行读取,每次读取后自动修改内部锁存器指针(指向存放下一个转换结束的数据锁存器)。当所有通道数据均读取后,内部锁存器指针自动复位(指向存放第一个转换结束的数据锁存器)。

根据上述AD7864的工作原理,DSP与AD7864的接口电路如图1所示。

AD7864的软硬选择信号/S SEL置低,这时被选择的转换通道就由硬件通道信号的状态来决定,由于需要对4路信号进行采样,所以把全部置高,即4路通道全部选通。

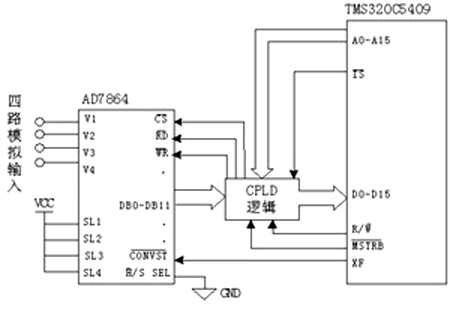

DSP与AD7864具体逻辑控制关系由CPLD来完成。CPLD部分逻辑关系图如图2。

AD7864的12位数据线DB0-DB11经过缓存与DSP数据线的低12位D0-D11相连,DSP另外高4位则始终为逻辑低;对于正数,这种数据扩展不会产生影响,而对于负数,则需要在软件上进行一定的处理。DSP的通用I/O引脚XF接到AD7864的引脚,XF信号由软件控制来启动AD7864的模数转换。DSP的I/O空间选择信号引脚和地址线A15的逻辑组合作为AD7864的片选信号。当有效,即为低电平时,如果地址线A15为低,则AD7864被片选。此时可以对AD7864进行读写操作,AD7864的地址为# 7FFF。DSP读写信号RW 和AD7864的片选信号的组合作为AD7864的读信号。当AD7864被片选,且RW为高时,就可以从AD7864读取数据,此时AD7864的写信号必须为高电平。DSP的存储器选通信号和读信号经过逻辑与后作为缓存的使能信号,分别控制DSP外部程序和A/D转换数据从缓存中送到DSP的数据总线上去。

图1 DSP与AD7864的接口电路

图2 CPLD内部控制逻辑电路

软件设计

DSP采样程序设计采用C和汇编语言混合编程的方式。TMS320C54x编译器可以利用asm语句将C54xDSP的汇编语言指令或伪指令直接嵌入编程器输出的汇编语言文件中。asm语句提供了C/C++语言不能提供的对DSP硬件的访问。利用asm语句拉低拉高XF引脚的输出信号来启动AD7864的模数转换,转换起始信号保持低电平的时间最少为35ns,整个转换过程所用的时间t为:t=X(tCONV+t9)-t9;其中,X为通道数,tCONV为单通道转换时间,当用内部时钟时,其最大值为1.65ms,t9为转换结束信号的脉冲宽度,最小值为75ns,最大值为180ns。同样利用asm语句执行汇编重复指令RPT,重复执行空操作NOP,达到比较精确的软件延时目的,这样做便于在满足基本转换时间的前提下,调节采样率的大小。4路信号全都完成转换模数后,DSP就可以从地址# 7FFF依次读取4路数据,在两次读取数据的过程中,需要一定的时间间隔。在读取完4路数据到下一次转换开始之间有一段静止时间,一般为50ns到100ns。

此外,DSP数据线有16位,而AD7864只有12位,并且数值都是以补码表示的,由于在硬件处理中把送到DSP数据线高4位上的数据都置为0,所以对于AD7864送给DSP的负数,要想在DSP中表示正确,还需要进行符号位扩展。具体办法就是对AD7864送给DSP的数据和0x800进行按位与运算,如果为真,则表示此数为负数,把此数和0xF000进行按位或运算,即在此数的高4位补上全1,这样负数就能在DSP中正确表示了。

- 使用 PlanAhead Design 工具提高设计性能(04-28)

- 基于ADSP-BF561的控制信号处理系统(05-11)

- 基于ADSP-BF537的视频SOC验证方案设计(05-18)

- ADSP-TSl01S嵌入式系统的混合编程(05-18)

- 基于DSP和ADS8364的高速数据采集处理系统(05-21)

- ADSP-TS201的系统设计及外部总线接口技术(06-25)