基于DSP和ADS8364的高速数据采集处理系统

随着现代科学技术的发展和计算机技术的普及,高速数据采集系统已应用于越来越多的场合,如通信、雷达、生物医学、机器人、语音和图像处理等领域。本文介绍的数据采集处理系统采用CPLD控制ADS8364|0">ADS8364完成数据的A/D转换,转换后的数据预先存储到FIFO中,再经DSP进行前端的数字信号处理后,通过USB总线传给上位机,并在上位机上进行存储、显示和分析等。该系统完全可以满足信号采集处理对高精度及实时性的要求。

1 系统原理

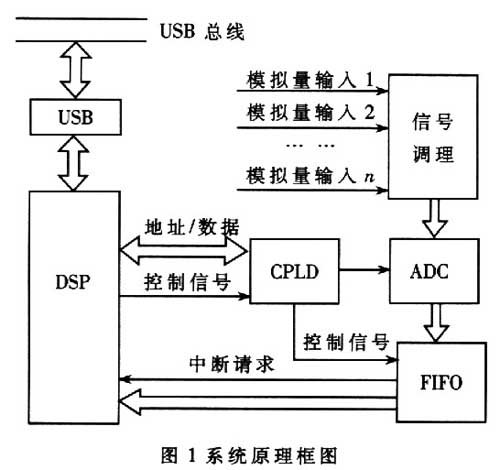

数据采集处理系统主要由前端信号调理电路、ADC芯片ADS8364、CPLD芯片EPM3128A、DSP芯片TMS320F2812、USB芯片CY7C68013及其外围电路组成。系统原理框图如图l所示。

系统主要完成的任务为:DSP接收上位机通过USB总线发送的命令,完成系统工作参数的设置,并通过模拟地址/数据总线与CPLD进行通信,向CPLD发送控制命令;对外部的多路模拟量输入进行信号调理,在CPLD控制下进行单通道或多通道A/D转换,将采集到的数据存储在一片FIFO芯片中;当FIFO中存储的数据半满时,对DSP产生一个中断信号,DSP收到此中断信号后,取出FIFO中的部分数据,进行前端数字信号处理,将处理完毕的数据通过USB总线传给上位机;上位机实现各种图形界面操作和后端信号处理,对所采集的信号进行分析。系统可对输入的多路模拟信号进行同步采样,这就使得采集到的数据不仅含有模拟信号的幅度特性,同时还保持不同模拟信号之间的相位差异;采样频率可以预置,以适应不同速率的采样要求。

2 系统硬件

系统硬件包括信号调理模块、A/D转换模块、DSP处理器模块、CPLD逻辑控制模块以及USB通信模块。

2.1 信号调理模块的设计

外部的多路模拟量输入信号往往是微弱的传感器信号,信号的幅值较小,为了方便且不失一般性,假定其幅值范围为O~25mV。ADS8364待转换的模拟输入电压范围应保持在AGND-0.3V和AVDD+O.3V之间。这里选用低功率变增益仪表放大器INAl29对模拟量输入信号进行调理放大,将其放大为0~5V之间。

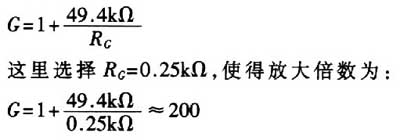

INAl29是BURR-BROWM公司的一种小功率通用仪表放大器,具有优异的精度和很宽的带宽,在增益高达100时,带宽达200kHz。它可用单一外部电阻器调节其增益,调节范围为l~10000,其放大倍数计算公式为:

从而使放大输出电压在O~5V之间。信号调理模块原理图如图2所示。

2.2 A/D转换模块的设计

该模块采用了TI公司的高速、低功耗、六通道同步采样模/教转换器ADS8364,它采用+5V工作电压,其6个模拟输入通道分为三组(A,B和C),每组都有一个ADCs保持信号(HOLDA,HOLDB和HOLDC),用来启动各组的AID转换,6个通道可以进行同步并行采样和转换。ADS8364采用具有80dB共模抑制能力的全差分输入通道,将其REFin和REFout引脚接到一起,为差分电路提供2.5V的参考电压。这里模拟量采用单端输入,将-IN端接共模电压2.5V,+IN端接前端信号调理模块的输出。

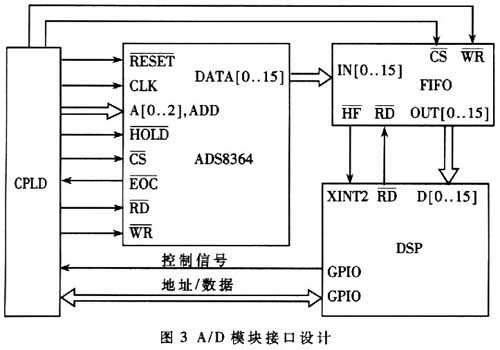

ADS8364的时钟信号由外部提供,最高频率为5MHz,对应的采样频率是250kHz。这里由CPLD提供时钟信号,主要是考虑到CPLD可以灵活地改变时钟频率,进而改变系统的采样频率。A/D转换完成后产生转换结束信号EOC。将ADS8364的。BYTE引脚接低电平,使转换结果以16位的方式输出。地址/模式信号(A0,Al,A2)决定ADS8364的数据读取方式,可以选择的方式包括单通道、周期或FIFO模式。将ADD引脚置为高电平,使得读出的数据中包含转换通道信息。考虑到数据采集处理系统的采样频率一般较高,如果用DSP直接控制ADS8364的访问,将占用DSP较多的资源,同时对DSP的实时性要求也较高。因此在本系统设计中,用CPLD实现ADS8364的接口控制电路,并将转换结果存储在FIFO芯片中,用DSP实现FIFO芯片的输出接口。

DSP、CPLD、ADS8364及FIFO之间的接口设计如图3所示。

2.3 DSP处理器模块的设计

DSP主要负责与USB通信模块交换数据、以模拟地址/数据总线的方式与CPLD通信,实现对数据采集的控制,完成与FIFO芯片的输出接口以及对采样后的数据进行前端数字信号处理(FIR低通滤波)。这里选用TI公司的32位定点DSP TMS320F2812 (以下简称F2812),它采用1.8V的内核电压,具有3.3V的外围接口电压,最高频率150MHz,片内有18K字的RAM,128K字的高速Flash。

2.4 CPLD逻辑控制模块的设计

在该数据采集处理系统中,CPLD是一个重要的组成部分。由CPLD组成的逻辑控制模块接收DSP传送过来的动作命令,控制A/D转换模块进行数据采集,并提供对FIFO的接口时序,实现转换数据的存储。这里选用Altem公司的EPM3128A芯片,它共有128个宏单元,2500个可用门。

CPLD作为一个单独的控制执行结构.通过编写相应的Verilog HDL代码,即可生成相应的操作电路,实现对各种输入信号的锁存、判断和处理以及对各种命令信号的执行和输出信号的控制。

2.5 USB通信模块的设计

这里选用CYPRESS公司的EZ-USB FX2系列中的CY7C68013作为USB通信控制器芯片,它内含增强型8051微控制器,支持USB2.0传输协议,同时也向下兼容USBl.1规范。该芯片把USB2.0收发器、SIE(串行接口引擎)、增强型8051微控制器、I2C总线接口以及GPIF(通用可编程接口)集成于一体。CY7C68013提供了SlaveFIFO和GPIF两种接口模式,Slave FIFO模式是从机模式,外部控制器可以像对普通FI

FO存储器一样对FX2的多层缓冲FIFO存储器进行读写;GPIF模式是主机模式,可以由软件设置读写的控制波形,灵活性很大。这里采用的是Slave FIFO模式。

- F1aSh存储器在TMS320C3X系统中的应用(11-11)

- 基于PIC18F系列单片机的嵌入式系统设计(11-19)

- DSP在卫星测控多波束系统中的应用(01-25)

- 基于PCI总线的双DSP系统及WDM驱动程序设计(01-26)

- 利用Virtex-5 FPGA实现更高性能的方法(03-08)

- DSP与单片机通信的多种方案设计(03-08)